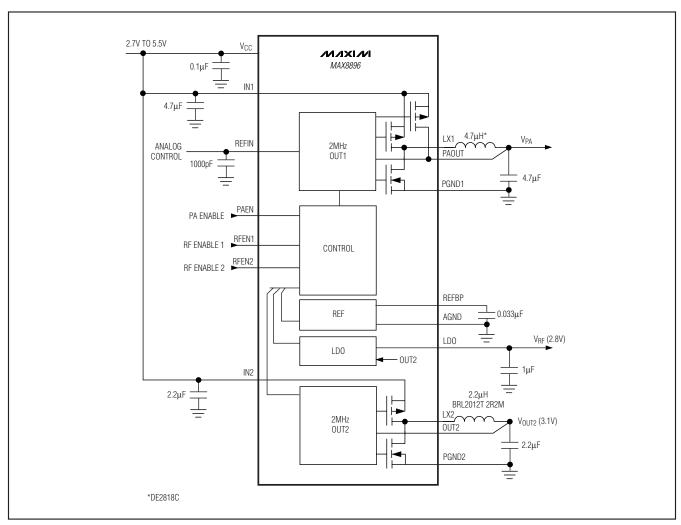

#### **General Description**

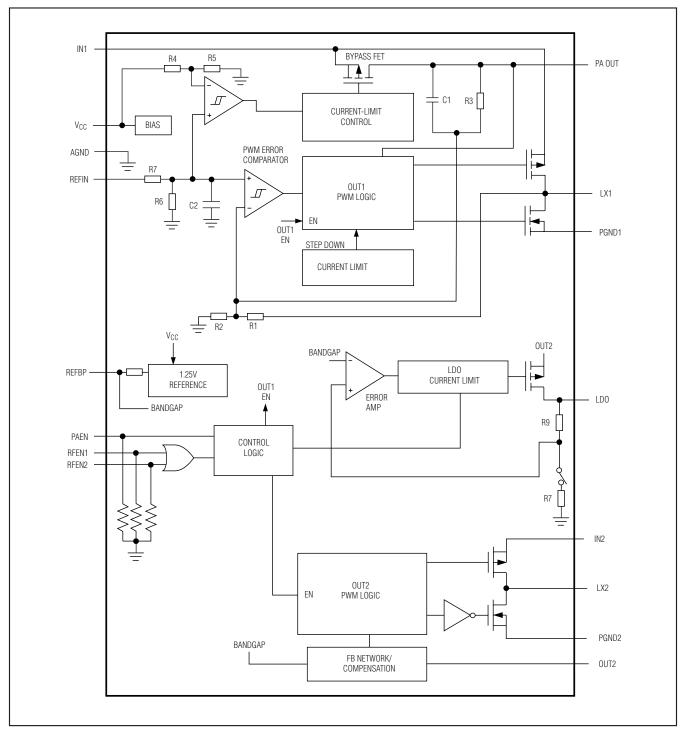

The MAX8896 dual step-down converter is optimized for powering the power amplifier (PA) and RF transceiver in WCDMA handsets. This device integrates a highefficiency PWM step-down converter (OUT1) for medium and low-power transmission, and a  $140m\Omega$ (typ) bypass FET to power the PA directly from the battery during high-power transmission. A second highefficiency PWM step-down converter (OUT2) supplies power directly to a high PSRR, low output noise, 200mA low-dropout linear regulator (LDO) to power the RF transceiver.

Fast switching allows the use of small ceramic input and output capacitors while maintaining low ripple voltage. The feedback network is integrated reducing external component count and total solution size. OUT1 uses an analog input driven by an external DAC to control the output voltage linearly for continuous PA power adjustment. At high duty cycle, OUT1 automatically switches to bypass mode, connecting the input to the output through a low-impedance (140m $\Omega$ , typ) MOSFET.

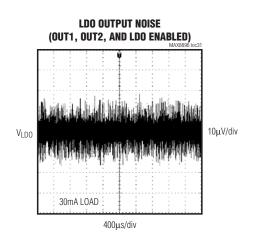

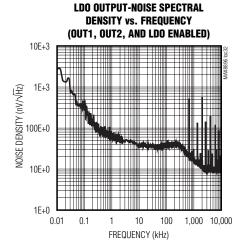

OUT2 is a 2MHz fixed-frequency, step-down converter capable of operating at 100% duty cycle. Output accuracy is ±2% over load, line, and temperature. The output of OUT2 is preset to 3.1V to provide power to a 200mA, 2.8V LDO designed for low noise (16µVRMS, typ), high PSRR (65dB, typ) operation. This configuration provides noise attenuation for the RF transceiver power supply in the 100Hz to 100kHz range.

Other features include separate output enables, lowsupply current shutdown, output overcurrent, and overtemperature protection. The MAX8896 is available in a 16-bump, 2mm x 2mm UCSP™ package (0.7mm max height).

**Applications**

WCDMA/NCDMA Cellular Handsets Smartphones

**Features**

- ◆ PA Step-Down Converter (OUT1)

- 7.5µs (typ) Settling Time for 0.5V to 1V Output Voltage Change

- Dynamic Output Voltage Setting from 0.5V to

- 140m $\Omega$  Bypass PFET and 100% Duty Cycle for Low Dropout

- 2MHz Switching Frequency

- Low Output Voltage Ripple

- 700mA (min) Output Drive Capability

- 2% Gain Accuracy

- **Tiny External Components**

- ♦ RF Step-Down Converter (OUT2)

- 2MHz Fixed Switching Frequency

- 94% Peak Efficiency

- 100% Duty Cycle

- 2% Output Accuracy Over Load, Line, and **Temperature**

- 200mA (min) Output Drive Capability

- **Tiny External Components**

- **♦ Low-Noise LDO**

- **Guaranteed 200mA Output**

- High 65dB (typ) PSRR

- **Fixed Output Voltage**

- Low Noise (16µVRMS, typ)

- **♦ Simple Logic ON/OFF Controls**

- ♦ Low 0.1µA Shutdown Current

- ♦ 2.7V to 5.5V Supply Voltage Range

- **♦ Thermal Shutdown**

- ◆ 2mm x 2mm UCSP Package (4 x 4 Grid)

#### **Ordering Information**

| PART          | PIN-PACKAGE           | LDO<br>VOLTAGE |

|---------------|-----------------------|----------------|

| MAX8896EREE+T | 16 UCSP (0.5mm pitch) | 2.80V          |

**Note:** Device operates over the -40°C to +85°C temperature

+Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

UCSP is a trademark of Maxim Integrated Products, Inc.

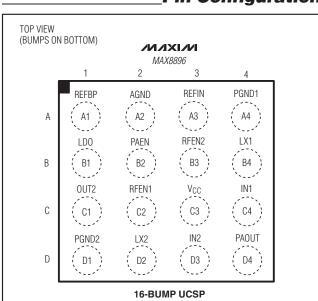

Pin Configurations appear at end of data sheet.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , IN1, IN2, PAEN, RFEN1, RFEN2, |                               |

|-------------------------------------------------|-------------------------------|

| REFIN, OUT2, REFBP to AGND                      | 0.3V to +6.0V                 |

| PAOUT to AGND                                   | 0.3V to $(V_{IN1} + 0.3V)$    |

| LDO to AGND                                     | $0.3V$ to $(V_{OUT2} + 0.3V)$ |

| IN1, IN2 to V <sub>C</sub> C                    | 0.3V to +0.3V                 |

| IN1 to IN2                                      | 0.3V to +0.3V                 |

| PGND1, PGND2 to AGND                            | 0.3V to +0.3V                 |

| LX1 Current                                     | 1A <sub>RMS</sub>             |

| LX2 Current                                     | 1A <sub>RMS</sub>             |

| IN1 and PAOUT Current                           | 1A <sub>RMS</sub>             |

|                                                 |                               |

| PAOUT, OUT2, LDO Short Circuit to PGND1,                    |

|-------------------------------------------------------------|

| PGND2Continuous                                             |

| Continuous Power Dissipation ( $T_A = +70$ °C)              |

| 16-Bump UCSP (derate 12.5mW/°C above +70°C)1W               |

| Junction-to-Ambient Thermal Resistance (θJA) (Note 1)96°C/W |

| Junction Temperature+150°C                                  |

| Storage Temperature Range65°C to +150°C                     |

| Bump Temperature (soldering, reflow)+260°C                  |

|                                                             |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{IN1} = V_{IN2} = V_{PAEN} = V_{RFEN1} = V_{RFEN2} = 3.6V$ ,  $V_{REFIN} = 0.72V$ ,  $T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , typical values are at  $T_{A} = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                      | CONDITIONS                                            |                                           |      | TYP               | MAX   | UNITS       |  |

|------------------------------------------------|-------------------------------------------------------|-------------------------------------------|------|-------------------|-------|-------------|--|

| INPUT SUPPLY                                   | ·                                                     |                                           | ·    |                   |       | •           |  |

| Input Voltage                                  | V <sub>CC</sub> , V <sub>IN1</sub> , V <sub>IN2</sub> |                                           |      |                   | 5.5   | V           |  |

| Input Undervoltage Threshold                   | V <sub>CC</sub> rising, 180mV typical hyste           | eresis                                    | 2.52 | 2.63              | 2.70  | V           |  |

| Chutdown Cupply Current                        | VPAEN = VRFEN1 = VRFEN2 = 0                           | $T_A = +25^{\circ}C$                      |      | 0.1               | 4     |             |  |

| Shutdown Supply Current                        | VPAEN = VRFEN1 = VRFEN2 = 0                           | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ |      | 0.1               |       | μA          |  |

| LOGIC CONTROL                                  |                                                       |                                           |      |                   |       |             |  |

| PAEN, RFEN1, RFEN2 Logic<br>Input High Voltage | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V                         |                                           | 1.3  |                   |       | V           |  |

| PAEN, RFEN1, RFEN2 Logic<br>Input Low Voltage  | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V                         | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V             |      |                   | 0.4   | V           |  |

| PAEN, RFEN1, RFEN2 Internal Pulldown Resistor  |                                                       |                                           |      | 800               | 1600  | kΩ          |  |

| PAEN, RFEN1, RFEN2 Logic                       |                                                       | T <sub>A</sub> = +25°C                    |      | 0.01              | 1     | <u>1</u> μΑ |  |

| Input Current                                  | V <sub>IL</sub> = 0                                   | T <sub>A</sub> = +85°C                    |      | 0.1               |       |             |  |

| REFBP                                          |                                                       |                                           |      |                   |       |             |  |

| REFBP Output Voltage                           | 0μA ≤ IREFBP ≤ 1μA                                    |                                           |      | 1.250             | 1.263 | V           |  |

| THERMAL PROTECTION                             |                                                       |                                           |      |                   |       |             |  |

| Thermal Shutdown                               | T <sub>A</sub> rising, 20°C typical hysteresis        |                                           |      | +160              |       | °C          |  |

| OUT1                                           |                                                       |                                           |      |                   |       |             |  |

| Quiescent Supply Current                       | VRFEN1 = VRFEN2 = 0V, IPA = 0A, no switching          |                                           |      | 155               |       | μΑ          |  |

| On Desistance                                  | p-channel MOSFET switch, I <sub>LX1</sub>             | T switch, $I_{LX1} = -200 \text{mA}$ 0.16 |      | 0.40              | 0     |             |  |

| On-Resistance                                  | n-channel MOSFET rectifier, I <sub>LX1</sub> = 500mA  |                                           |      | 0.17              | 0.40  | Ω           |  |

| Load Regulation                                | R <sub>L</sub> is the inductor resistance             |                                           |      | R <sub>L</sub> /2 |       | V/A         |  |

| LV1 Lookaga Current                            | Vivia E EV Vivia OV                                   | T <sub>A</sub> = +25°C                    |      | 0.1               | 5     |             |  |

| LX1 Leakage Current                            | $V_{IN1} = 5.5V, V_{LX1} = 0V$                        | T <sub>A</sub> = +85°C                    |      | 1                 |       | μΑ          |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{IN1} = V_{IN2} = V_{PAEN} = V_{RFEN1} = V_{RFEN2} = 3.6V, V_{REFIN} = 0.72V, T_A = -40^{\circ}C$  to +85°C, typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | CONDITIONS                                                                           |                                           | MIN   | TYP                       | MAX   | UNITS |

|-----------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------|-------|---------------------------|-------|-------|

| Peak Current Limit (p-Channel MOSFET)   |                                                                                      |                                           | 1200  | 1450                      | 1700  | mA    |

| Valley Current Limit (n-Channel MOSFET) |                                                                                      |                                           | 1100  | 1350                      | 1600  | mA    |

| Minimum On-Time                         |                                                                                      |                                           |       | 70                        |       | ns    |

| Minimum Off-Time                        |                                                                                      |                                           |       | 50                        |       | ns    |

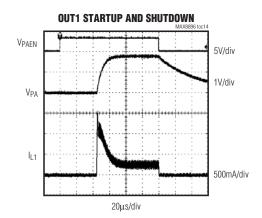

| Power-Up Delay                          | From VPAEN rising to VLX1 ri                                                         | sing                                      |       | 50                        | 75    | μs    |

| OUT1 REFIN                              |                                                                                      |                                           |       |                           |       |       |

| Common-Mode Range                       |                                                                                      |                                           | 0.2   |                           | 1.7   | V     |

| REFIN-to-PAOUT Gain                     | V <sub>REFIN</sub> = 0.32V or 1.32V, I <sub>L</sub>                                  | x1 = 0A                                   | 2.45  | 2.5                       | 2.55  |       |

| Input Resistance                        |                                                                                      |                                           |       | 320                       |       | kΩ    |

| BYPASS                                  |                                                                                      |                                           | •     |                           |       | •     |

| Bypass Mode Threshold                   | V <sub>REFIN</sub> falling, 150mV hyste                                              | resis                                     |       | 0.396<br>xV <sub>CC</sub> |       | V     |

| 0. D                                    | p-channel MOSFET                                                                     | T <sub>A</sub> = +25°C                    |       | 0.14                      |       |       |

| On-Resistance                           | $I_{OUT} = -90mA$                                                                    | T <sub>A</sub> = +85°C                    |       | 0.3                       |       | Ω     |

| Bypass Current Limit                    | VPAOUT = 1.5V                                                                        |                                           | 700   | 1000                      | 1400  | mA    |

| Step-Down Current Limit in Bypass       |                                                                                      |                                           | 1200  | 1450                      | 1700  | mA    |

| Total Bypass Current Limit              | $V_{PAOUT} = V_{LX1} = 1.5V$                                                         |                                           | 1900  | 2450                      | 3100  | mA    |

| Bypass Off-Leakage Current              | V <sub>CC</sub> = V <sub>IN1</sub> = 5.5V,<br>V <sub>PAOUT</sub> = 0V                | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ |       | 0.01                      | 5     | μΑ    |

| OUT2                                    |                                                                                      |                                           |       |                           |       |       |

| Output Voltage                          | I <sub>OUT2</sub> = 0 to 150mA,<br>V <sub>IN2</sub> = V <sub>CC</sub> = 3.2V to 4.5V |                                           | 3.038 | 3.1                       | 3.162 | V     |

| OUT2 Leakage Current                    | VRFEN1 = VRFEN2 = 0                                                                  | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ |       | 0.01                      | 5     | μΑ    |

| No-Load Supply Current                  | VPAEN = 0V, IOUT2 = 0A, sw                                                           | vitching                                  |       | 2.5                       |       | mA    |

| 0. D. : .                               | p-channel MOSFET switch, I <sub>LX2</sub> = -40mA                                    |                                           |       | 300                       |       | mΩ    |

| On-Resistance                           | n-channel MOSFET rectifier, I <sub>LX2</sub> = 40mA                                  |                                           |       | 300                       |       | mΩ    |

| p-Channel Current-Limit<br>Threshold    |                                                                                      |                                           | 400   | 450                       | 500   | mA    |

| n-Channel Negative Current Limit        |                                                                                      |                                           |       | 400                       |       | mA    |

| Maximum Duty Cycle                      |                                                                                      |                                           |       | 100                       |       | %     |

| Minimum Duty Cycle                      |                                                                                      |                                           |       | 16.5                      |       | %     |

| PWM Frequency                           |                                                                                      |                                           | 1.8   | 2.0                       | 2.2   | MHz   |

| Power-Up Delay                          | From V <sub>RFEN1</sub> or V <sub>RFEN2</sub> rising to V <sub>LX2</sub> rising      |                                           |       | 35                        | 75    | μs    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{IN1} = V_{IN2} = V_{PAEN} = V_{RFEN2} = 3.6V, \ V_{REFIN} = 0.72V, \ T_{A} = -40^{\circ}C \ to \ +85^{\circ}C, \ typical \ values \ are \ at \ T_{A} = +25^{\circ}C, \ unless \ otherwise \ noted.) \ (Note 2)$

| PARAMETER                                                                      | PARAMETER CONDITIONS                                                            |       |       |       | UNITS             |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| LDO                                                                            |                                                                                 |       |       |       |                   |

| Output Voltage, V <sub>LDO</sub>                                               | V <sub>OUT2</sub> = 3.1V, I <sub>LDO</sub> = 1mA to 200mA                       | 2.744 | 2.800 | 2.856 | V                 |

| Current Limit                                                                  | $V_{OUT2} = 3.1V, V_{LDO} = 0V$                                                 | 250   | 420   | 750   | mA                |

| Dropout Voltage                                                                | V <sub>OUT2</sub> = 3.1V, I <sub>LDO</sub> = 100mA                              |       | 70    |       | mV                |

| Line Regulation                                                                | V <sub>OUT2</sub> stepped from 3.5V to 5.5V, I <sub>LDO</sub> = 100mA           |       | 2.4   |       | mV                |

| Load Regulation                                                                | V <sub>OUT2</sub> = 3.1V, I <sub>LDO</sub> stepped from 50μA to 200mA           | 25    |       | mV    |                   |

| Power-Supply Rejection<br>ΔV <sub>LDO</sub> /ΔV <sub>OUT2</sub>                | $V_{OUT2} = 3.1V$ , 10Hz to 10kHz,<br>$C_{LDO} = 1\mu F$ , $I_{LDO} = 100mA$    |       | 65    |       | dB                |

| Output Noise                                                                   |                                                                                 |       | 16    |       | μV <sub>RMS</sub> |

| Minimum Output Capacitance for Stable Operation 0 < I <sub>LDO</sub> < 200mA 1 |                                                                                 |       | μF    |       |                   |

| Output Leakage Current                                                         | V <sub>OUT2</sub> = 3.1V, V <sub>RFEN1</sub> = V <sub>RFEN2</sub> = 0V          | 25    |       | nA    |                   |

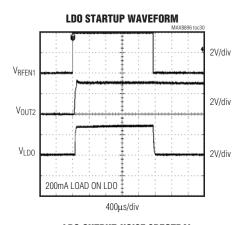

| Power-Up Delay                                                                 | From V <sub>RFEN1</sub> or V <sub>RFEN2</sub> rising to V <sub>LDO</sub> rising | 50    |       |       | μs                |

Note 2: All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

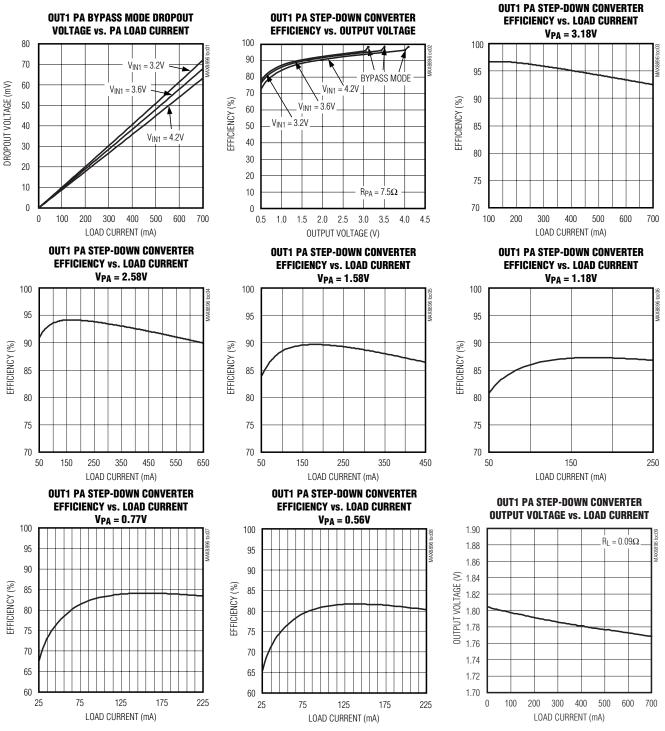

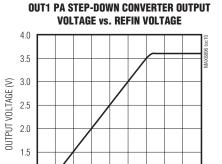

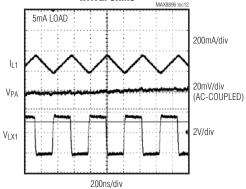

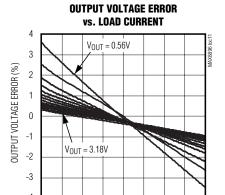

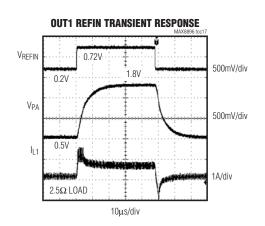

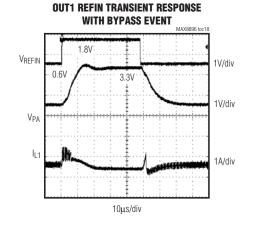

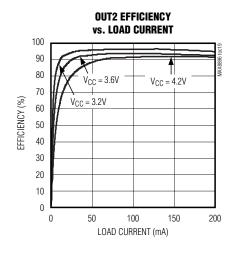

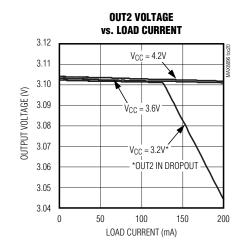

#### Typical Operating Characteristics

$(V_{CC} = V_{IN1} = V_{IN2} = 3.6V, V_{REFIN} = 0.72V, circuit of Figure 3, T_A = +25°C, unless otherwise noted.)$

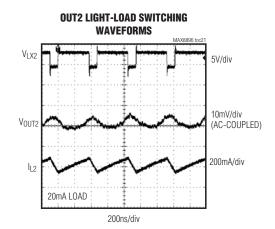

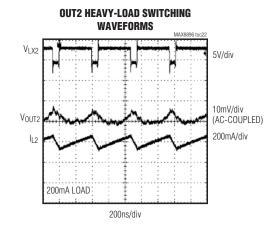

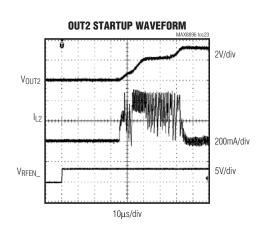

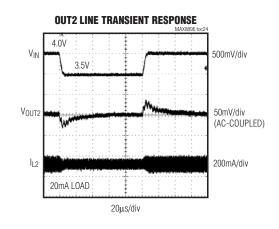

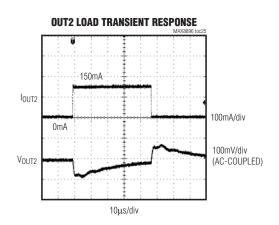

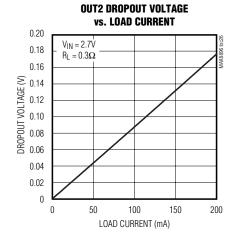

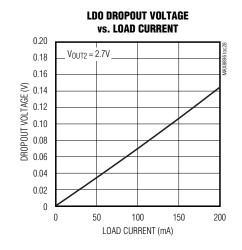

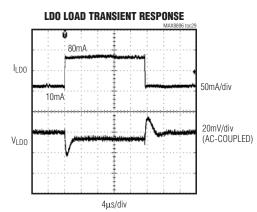

#### Typical Operating Characteristics (continued)

$(V_{CC} = V_{IN1} = V_{IN2} = 3.6V, V_{REFIN} = 0.72V, circuit of Figure 3, T_A = +25$ °C, unless otherwise noted.)

1.0

0.5

OUT1 LIGHT-LOAD SWITCHING WAVEFORMS

$0.2 \quad 0.4 \quad 0.6 \quad 0.8 \quad 1.0 \quad 1.2 \quad 1.4 \quad 1.6 \quad 1.8 \quad 2.0$

REFIN VOLTAGE (V)

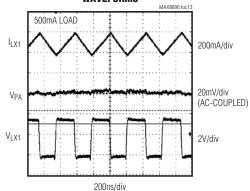

OUT1 HEAVY-LOAD SWITCHING WAVEFORMS

LOAD CURRENT (mA)

0

100 200 300 400 500 600 700 800

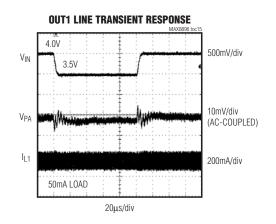

#### Typical Operating Characteristics (continued)

(V<sub>CC</sub> = V<sub>IN1</sub> = V<sub>IN2</sub> = 3.6V, V<sub>RFFIN</sub> = 0.72V, circuit of Figure 3, T<sub>A</sub> = +25°C, unless otherwise noted.)

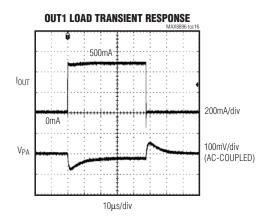

#### Typical Operating Characteristics (continued)

$(V_{CC} = V_{IN1} = V_{IN2} = 3.6V, V_{REFIN} = 0.72V, circuit of Figure 3, T_A = +25^{\circ}C, unless otherwise noted.)$

#### Typical Operating Characteristics (continued)

$(V_{CC} = V_{IN1} = V_{IN2} = 3.6V, V_{REFIN} = 0.72V,$  circuit of Figure 3,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

#### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                        |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | REFBP | Reference Noise Bypass. Bypass REFBP to AGND with a $0.033\mu F$ ceramic capacitor to reduce noise on the LDO output. REFBP is internally pulled down through a $1k\Omega$ resistor during shutdown.                                                                                                            |

| A2  | AGND  | Low-Noise Analog Ground. Connect AGND to the ground plane at a single point away from high switching currents. See the <i>PCB Layout</i> section.                                                                                                                                                               |

| А3  | REFIN | DAC-Controlled Input. The output of the PA step-down converter is regulated to 2.5 x $V_{REFIN}$ . When $V_{REFIN}$ reaches 0.396 x $V_{CC}$ , bypass mode is enabled.                                                                                                                                          |

| A4  | PGND1 | Power Ground for OUT1. Connect PGND1 to the ground plane near the input and output capacitor grounds. See the <i>PCB Layout</i> section.                                                                                                                                                                        |

| B1  | LDO   | 200mA LDO Regulator Output. Bypass LDO with a 1µF ceramic capacitor as close as possible to LDO and ground. Leave LDO unconnected if not used.                                                                                                                                                                  |

| B2  | PAEN  | OUT1 Enable Input. Connect PAEN to IN1 or logic-high for normal operation. Connect to ground or logic-low to shut down OUT1. Internally connected to ground through an $800k\Omega$ resistor.                                                                                                                   |

| В3  | RFEN2 | OUT2 and LDO Enable Input. Connect RFEN1 or RFEN2 to IN2 or logic-high for normal operation. Connect RFEN1 and RFEN2 to ground or logic-low to shut down OUT2 and the LDO. Internally connected to ground through an $800k\Omega$ resistor.                                                                     |

| B4  | LX1   | Inductor Connection. Connect an inductor from LX1 to the output of OUT1.                                                                                                                                                                                                                                        |

| C1  | OUT2  | Output of OUT2. OUT2 is also the supply voltage input for the LDO. Bypass OUT2 with a 2.2µF ceramic capacitor as close as possible to OUT2 and PGND2.                                                                                                                                                           |

| C2  | RFEN1 | OUT2 and LDO Enable Input. Connect RFEN1 or RFEN2 to IN2 or logic-high for normal operation. Connect RFEN1 and RFEN2 to ground or logic-low to shut down OUT2 and the LDO. Internally connected to ground through an $800 k\Omega$ resistor.                                                                    |

| C3  | Vcc   | Supply Voltage Input for Internal Reference and Control Circuitry. Connect V <sub>CC</sub> to a battery or supply voltage from 2.7V to 5.5V. Bypass V <sub>CC</sub> with a 0.1µF ceramic capacitor as close as possible to V <sub>CC</sub> and AGND. Connect V <sub>CC</sub> , IN1, and IN2 to the same source. |

| C4  | IN1   | Supply Voltage Input for OUT1. Connect IN1 to a battery or supply voltage from 2.7V to 5.5V. Bypass IN1 with a 4.7µF ceramic capacitor as close as possible to IN1 and PGND1. Connect IN1, V <sub>CC</sub> , and IN2 to the same source.                                                                        |

| D1  | PGND2 | Power Ground for OUT2. Connect PGND2 to the ground plane near the input and output capacitor grounds. See the <i>PCB Layout</i> section.                                                                                                                                                                        |

| D2  | LX2   | Inductor Connection. Connect an inductor from LX2 to the output of OUT2.                                                                                                                                                                                                                                        |

| D3  | IN2   | Supply Voltage Input for OUT2. Connect IN2 to a battery or supply voltage from 2.7V to 5.5V. Bypass IN2 with a 2.2µF ceramic capacitor as close as possible to IN2 and PGND2. Connect IN2, V <sub>CC</sub> , and IN1 to the same source.                                                                        |

| D4  | PAOUT | PA Connection for Bypass Mode. Internally connected to IN1 using the internal bypass MOSFET during bypass mode. PAOUT is internally connected to the feedback network for OUT1. Bypass PAOUT with a 4.7µF ceramic capacitor as close as possible to PAOUT and PGND1.                                            |

Figure 1. Block Diagram

#### **Detailed Description**

The MAX8896 dual step-down converter is optimized for powering the power amplifier (PA) and RF transceiver in WCDMA handsets. This device integrates a highefficiency PWM step-down converter (OUT1) for medium and low-power transmission, and a  $140m\Omega$  (typ) bypass FET to power the PA directly from the battery during high power transmission. A second highefficiency PWM step-down converter (OUT2) supplies power directly to a high PSRR, low-output noise, 200mA low-dropout linear regulator (LDO) to power the RF transceiver.

#### **OUT1 Step-Down Converter**

A hysteretic PWM control scheme ensures high efficiency, fast switching, fast transient response, low output ripple, and physically tiny external components. The control scheme is simple: when the output voltage is below the regulation threshold, the error comparator begins a switching cycle by turning on the high-side switch. This high-side switch remains on until the minimum on-time expires and output voltage is within regulation, or the inductor current is above the current-limit threshold. Once off, the high-side switch remains off until the minimum off-time expires and the output voltage falls again below the regulation threshold. During the off period, the low-side synchronous rectifier turns on and remains on until the high-side switch turns on again. The internal synchronous rectifier eliminates the need for an external Schottky diode.

#### Voltage-Positioning Load Regulation

The MAX8896 step-down converter utilizes a unique feedback network. By taking DC feedback from the LX node through R1 of Figure 1, the usual phase lag due to the output capacitor is removed, making the loop exceedingly stable and allowing the use of very small ceramic output capacitors. To improve the load regulation, resistor R3 is included in the feedback. This configuration yields load regulation equal to half the inductor's series resistance multiplied by the load current. This voltage-positioning load regulation greatly reduces overshoot during load transients or when changing the output voltage from one level to another. However, when calculating the required REFIN voltage, the load regulation should be considered. Because inductor resistance is typically well specified and the typical PA is a resistive load, the V<sub>REFIN</sub> to V<sub>OUT1</sub> gain is slightly less than 2.5V/V. The output voltage is approximately:

$$V_{OUT1} = 2.5 \times V_{REFIN} - \frac{1}{2} \times R_{L} \times I_{LOAD}$$

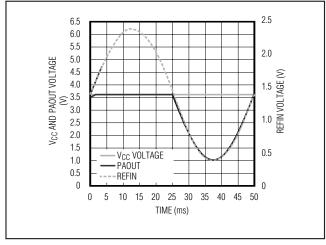

#### Automatic Bypass Mode

During high-power transmission, the bypass mode connects IN1 directly to PAOUT with the internal  $140m\Omega$  (typ) bypass FET, while the step-down converter is forced into 100% duty-cycle operation. The low onresistance in this mode provides low dropout, long battery life, and high output current capability. OUT1 enters bypass mode automatically when VREFIN > 0.396 x VCC (see Figure 2). Current-limit circuitry continuously limits current through the bypass FET to 1000mA (typ). The bypass FET opens up if the voltage at PAOUT drops below 1.25V (typ) in current limit.

#### **OUT2 Step-Down Converter**

OUT2 is a high-efficiency, 2MHz current-mode step-down DC-DC converter that outputs 200mA with efficiency up to 94%. The output voltage of the MAX8896 is a fixed 3.1V for powering the LDO. RFEN1 and RFEN2 are dedicated enable inputs for OUT2. Drive RFEN1 or RFEN2 high to enable OUT2, or drive RFEN1 and RFEN2 low to disable OUT2. RFEN1 and RFEN2 have hysteresis so that an RC may be used to implement manual sequencing with respect to other inputs.

OUT2 operates with a constant 2MHz switching frequency regardless of output load. The MAX8896 regulates the output voltage by modulating the switching duty cycle. An internal n-channel synchronous rectifier eliminates the need for an external Schottky diode and improves efficiency. The synchronous rectifier turns on during the second half of each switching cycle (offtime). During this time, the voltage across the inductor is reversed, and the inductor current ramps down. The synchronous rectifier turns off at the end of the switching cycle.

Figure 2. Automatic Bypass

The OUT2 step-down DC-DC converter operates with 100% duty cycle when the supply voltage approaches the output voltage. This allows this converter to maintain regulation until the input voltage falls below the desired output voltage plus the dropout voltage specification of the converter. During 100% duty cycle operation, the high-side p-channel MOSFET turns on constantly, connecting the input to the output through the inductor. The dropout voltage (VDO) is calculated as follows:

$V_{DO} = I_{LOAD} \times (R_P + R_L)$

where:

Rp = internal p-channel MOSFET switch on-resistance (see *Electrical Characteristics*)

R<sub>I</sub> = external inductor DC resistance

#### **LDO**

The LDO provides 200mA at 2.8V and is designed for low noise ( $16\mu V_{RMS}$ , typ) and high PSRR (65dB, typ). The LDO is powered from OUT2 (3.1V) and is enabled or disabled at the same time as OUT2 using RFEN1 or RFEN2.

#### LDO Dropout Voltage

The regulator's minimum input/output differential (or dropout voltage) determines the lowest usable supply voltage. In battery-powered systems, this determines the useful end-of-life battery voltage. Because the LDO uses a p-channel MOSFET pass transistor, the dropout voltage is drain-to-source on-resistance (RDS(ON)) multiplied by the load current (see the *Typical Operating Characteristics*).

#### **Shutdown Mode**

Connect PAEN to GND or logic-low to place OUT1 in shutdown mode. In shutdown, the control circuitry, internal switching MOSFET, and synchronous rectifier turn off and LX1 becomes high impedance. Connect PAEN to IN1,  $V_{CC}$ , or logic-high for normal operation.

Either RFEN1 or RFEN2 enable OUT2 and the LDO. Connect RFEN1 and RFEN2 to GND or logic-low to place OUT2 and the LDO in shutdown mode. In shutdown, the control circuitry, internal switching MOSFET, and synchronous rectifier turn off and LX2 and the LDO output become high impedance. Connect RFEN1 or RFEN2 to IN2, VCC, or logic-high for normal operation. When PAEN, RFEN1, and RFEN2 are all logic-low, the MAX8896 enter a very low power state, where the input current drops to 0.1µA (typ).

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the MAX8896. If the junction temperature exceeds +160°C, the MAX8896 turn off, allowing the IC to cool. The IC turns on and begins soft-start after the junction temperature cools by 20°C. This results in a pulsed output during continuous thermal-overload conditions.

#### \_Applications Information

#### **Inductor Selection**

OUT1 operates with a switching frequency of 2MHz and utilizes a  $2.2\mu\text{H}$  to  $4.7\mu\text{H}$  inductor. OUT2 operates with a switching frequency of 2MHz and utilizes a  $2.2\mu\text{H}$  inductor. This operating frequency allows the use of physically small inductors while maintaining high efficiency.

The OUT1 inductor's DC current rating only needs to match the maximum load of the application because OUT1 features zero current overshoot during startup and load transients. For optimum transient response and high efficiency, choose an inductor with DC series resistance in the  $50 \text{m}\Omega$  to  $150 \text{m}\Omega$  range. See Table 1 for suggested inductors and manufacturers.

Using a larger inductance value reduces the ripple current, therefore providing higher efficiency at light load.

#### **Output Capacitor Selection**

For OUT1 and OUT2, the output capacitor keeps the output voltage ripple small and ensures regulation loop stability. Cout must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R temperature characteristics are highly recommended due to their small size, low ESR, and small temperature coefficients. A 4.7µF capacitor is recommended for Cout1 and 2.2µF is recommended for Cout2. For optimum load-transient performance and very low output ripple, the output capacitor value can be increased.

For the LDO, the minimum output capacitance required is dependent on the load currents. For loads lighter than 10mA, it is sufficient to use a 0.1µF capacitor for stable operation over the full temperature range. With rated maximum load currents, a minimum of 1µF is recommended. Larger value output capacitors further reduce output noise and improve load-transient response, stability, and power-supply rejection.

Note that some ceramic dielectrics exhibit large capacitance and ESR variation with temperature and DC bias. Ceramic capacitors with Z5U or Y5V temperature characteristics should be avoided. These regulators are optimized for ceramic capacitors. Tantalum capacitors are not recommended.

Figure 3. Typical Applications Circuit

#### **Input Capacitor Selection**

The input capacitor (C<sub>IN</sub>) reduces the current peaks drawn from the battery or input power source and reduces switching noise in the MAX8896. The impedance of C<sub>IN</sub> at the switching frequency should be kept very low. Ceramic capacitors with X5R or X7R temperature characteristics are highly recommended due to their small size, low ESR, and small temperature coefficients. A  $4.7\mu F$  capacitor is recommended for C<sub>IN1</sub> and  $2.2\mu F$  for C<sub>IN2</sub>. For optimum noise immunity and low input ripple, the input capacitor value can be increased.

Note that some ceramic dielectrics exhibit large capacitance and ESR variation with temperature and DC bias. Ceramic capacitors with Z5U or Y5V temperature characteristics should be avoided.

#### **Thermal Considerations**

In most applications, the MAX8896 does not dissipate much heat due to its high efficiency. But in applications where the MAX8896 runs at high ambient temperature with heavy loads, the heat dissipated may exceed the maximum junction temperature of the part. If the junction temperature reaches approximately +160°C, the thermal-overload protection is activated.

The MAX8896 maximum power dissipation depends on the thermal resistance of the IC package and circuit board, the temperature difference between the die junction and ambient air, and the rate of airflow. The power dissipated in the device is:

$PD = POUT1 \times (1/\eta OUT1 - 1) + POUT2 \times (1/\eta OUT2 - 1) + ILDO \times (VOUT2 - VLDO)$

where  $\eta$  is the efficiency of the step-down converter and  $P_{OUT}$  is the output power of the step-down converter. The maximum allowed power dissipation is:

$P_{MAX} = (T_{JMAX} - T_{A})/\theta_{JA}$

where (T<sub>JMAX</sub> - T<sub>A</sub>) is the temperature difference between the MAX8896 die junction and the surrounding air,  $\theta_{JA}$  is the thermal resistance of the junction through the PCB, copper traces, and other materials to the surrounding air.

**PCB Lavout**

High switching frequencies and relatively large peak currents make the PCB layout a very important part of design. Good design minimizes excessive EMI on the feedback paths and voltage gradients in the ground plane, resulting in a stable and well regulated output. Connect C<sub>IN1</sub> close to IN1 and PGND1 and connect C<sub>IN2</sub> close to IN2 and PGND2. Connect the inductor and output capacitor as close as possible to the IC and keep their traces short, direct, and wide. Keep noisy traces, such as the LX node, as short as possible. Refer to the MAX8896EVKIT for an example layout.

**Table 1. Suggested Inductors**

| MANUFACTURER | SERIES    | INDUCTANCE<br>(µH) | ESR<br>(Ω)           | CURRENT RATING (mA)  | DIMENSIONS                                                                        |

|--------------|-----------|--------------------|----------------------|----------------------|-----------------------------------------------------------------------------------|

|              | CB2016T   | 1.0<br>2.2         | 0.09<br>0.13         | 600<br>510           | 2.0mm x $1.6$ mm x $1.8$ mm = $5.8$ mm <sup>3</sup>                               |

| T : V I      | CB2518T   | 2.2<br>4.7         | 0.09<br>0.13         | 510<br>340           | $2.5 \text{mm} \times 1.8 \text{mm} \times 2.0 \text{mm}$<br>= $9 \text{mm}^3$    |

| Taiyo Yuden  | BRL2012T  | 2.2                | 0.30                 | 550                  | 2.0mm x 1.25mm x 1.0mm<br>= 2.5mm <sup>3</sup>                                    |

|              | CKP2520   | 2.2                | 0.09                 | 1300                 | 2.5mm x 2.0mm x 1.0mm<br>= 5mm <sup>3</sup>                                       |

| FDK          | MIPF2520  | 1.0<br>1.5<br>2.2  | 0.05<br>0.07<br>0.08 | 1500<br>1500<br>1300 | 2.5mm x 2.0mm x 1.0mm<br>= 5mm <sup>3</sup>                                       |

|              | MIPF2016  | 2.2                | 0.11                 | 1100                 | 2.0mm x 1.6mm x 1.0mm<br>= 3.2mm <sup>3</sup>                                     |

| Murata       | LQH32C_53 | 1.0<br>2.2         | 0.06<br>0.10         | 1000<br>790          | $3.2 \text{mm} \times 2.5 \text{mm} \times 1.7 \text{mm}$<br>= $14 \text{mm}^3$   |

|              | D3010FB   | 1.0                | 0.20                 | 1170                 | $3.0 \text{mm} \times 3.0 \text{mm} \times 1.0 \text{mm}$<br>= $9 \text{mm}^3$    |

|              | D2812C    | 1.2<br>2.2         | 0.09<br>0.15         | 860<br>640           | $3.0 \text{mm} \times 3.0 \text{mm} \times 1.2 \text{mm}$<br>= $11 \text{mm}^3$   |

| токо         | D310F     | 1.5<br>2.2         | 0.13<br>0.17         | 1230<br>1080         | 3.6mm x $3.6$ mm x $1.0$ mm = $13$ mm <sup>3</sup>                                |

|              | D312C     | 1.5<br>2.2         | 0.10<br>0.12         | 1290<br>1140         | 3.6mm x $3.6$ mm x $1.2$ mm = $16$ mm <sup>3</sup>                                |

|              | DE2818C   | 4.7                | 72                   | 950                  | $3.2 \text{mm} \times 3.0 \text{mm} \times 1.8 \text{mm}$<br>= $17.3 \text{mm}^3$ |

| 0            | CDRH2D09  | 1.2<br>1.5<br>2.2  | 0.08<br>0.09<br>0.12 | 590<br>520<br>440    | $3.0 \text{mm} \times 3.0 \text{mm} \times 1.0 \text{mm}$<br>= $9 \text{mm}^3$    |

| Sumida       | CDRH2D11  | 1.5<br>2.2<br>3.3  | 0.05<br>0.08<br>0.10 | 680<br>580<br>450    | 3.2mm x 3.2mm x 1.2mm<br>= 12mm <sup>3</sup>                                      |

| Coilcraft    | LPO3310   | 1.0<br>1.5<br>2.2  | 0.07<br>0.10<br>0.13 | 1600<br>1400<br>1100 | 3.3mm x 3.3mm x 1.0mm<br>= 11mm <sup>3</sup>                                      |

|              | XPL2010   | 4.7                | 0.284                | 740                  | 1.9mm x 2.0mm x 1.0mm<br>= 3.8mm <sup>3</sup>                                     |

| David        | ELC3FN    | 1.0<br>2.2         | 0.08<br>0.12         | 1400<br>1000         | $3.2 \text{mm} \times 3.2 \text{mm} \times 1.2 \text{mm}$<br>= $12 \text{mm}^3$   |

| Panasonic    | ELL3GM    | 1.0<br>2.2         | 0.07<br>0.10         | 1400<br>1100         | 3.2mm x 3.2mm x 1.5mm<br>= 15mm <sup>3</sup>                                      |

# MAX8896

# Dual PWM Step-Down Converter in a 2mm x 2mm Package for WCDMA PA and RF Power

#### Pin Configuration

\_\_\_\_\_Chip Information

PROCESS: BICMOS

#### \_Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 16 UCSP      | R162A2+1     | <u>21-0226</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.