# VERY LOW POWER 1.8V 16K/8K/4K X 16 DUAL-PORT **STATIC RAM**

### Features

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- ٠ Both ports configurable to standard SRAM or timemultiplexed address/data interface

#### ٠ High-speed access

- Industrial: 65ns (max.), ADM mode

- Industrial: 40ns (max.), Standard SRAM mode

- Low-power operation IDT70P269/259/249L Active: 27mW (typ.) Standby: 3.6µW (typ.)

- Supports 3.0V, 2.5V and 1.8V I/O's

- Power supply isolation functionality to aid system power ٠ management

- Separate upper-byte and lower-byte control

- ٠ Input Read Register

- ٠ **Output Drive Register**

- ٠ **BUSY** and Interrupt Flag

- ٠ On-chip port arbitration logic

- ٠ Fully asynchronous operation from either port

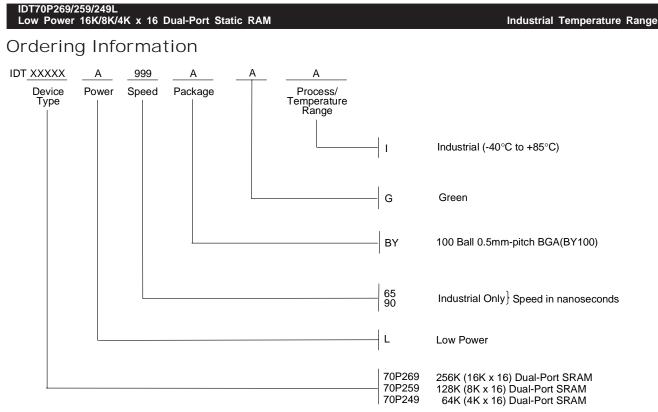

- ٠ Available in 100 Ball 0.5mm-pitch BGA

- ٠ Industrial temperature range (-40°C to +85°C)

- ٠ Green parts available, see ordering information

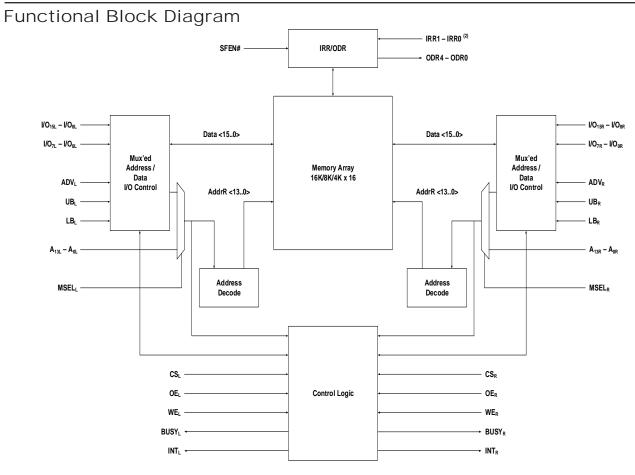

7146 drw 01

#### NOTES:

- 1. A13 A0 for IDT70P269; A12 A0 for IDT70P259; A11 A0 for IDT70P249.

- 2 IRR0 and IRR1 are not available for IDT70P269.

DSC-7146/1

# Description

The IDT70P269/259/249 is a very low power 16K/8K/4K x 16 Dual-Port Static RAM. The IDT70P269/259/249 is designed to be used as a stand-alone 256/128/64K-bit Dual-Port SRAM.

This device provides two independent ports with separate control, address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. An automatic power down feature controlled by  $\overline{CS}$  permits the on-chip circuitry of each port to enter a very low standby power mode.

# Pin Configurations<sup>(2,3)</sup>

# 70P269/259/249BY BYG-100

# 100-Ball 0.5mm Pitch BGA Top View

|   | 1                | 2                | 3                 | 4                               | 5                                  | 6                                  | 7                   | 8                  | 9                  | 10                 |   |

|---|------------------|------------------|-------------------|---------------------------------|------------------------------------|------------------------------------|---------------------|--------------------|--------------------|--------------------|---|

| A | A <sub>5R</sub>  | A <sub>8R</sub>  | A <sub>11R</sub>  | $\overline{UB}_R$               | V <sub>SS</sub>                    | $\overline{\text{ADV}}_{\text{R}}$ | I/O <sub>15R</sub>  | I/O <sub>12R</sub> | I/O <sub>10R</sub> | V <sub>ss</sub>    | А |

| В | A <sub>3R</sub>  | $A_{4R}$         | A <sub>7R</sub>   | A <sub>9R</sub>                 | $\overline{CS}_{R}$                | $\overline{WE}_{R}$                | $\overline{OE}_{R}$ | V <sub>DDIOR</sub> | I/O <sub>9R</sub>  | I/O <sub>6R</sub>  | В |

| С | A <sub>0R</sub>  | A <sub>1R</sub>  | A <sub>2R</sub>   | A <sub>6R</sub>                 | $\overline{LB}_{R}$                | IRR <sub>1</sub> <sup>(1)</sup>    | I/O <sub>14R</sub>  | I/O <sub>11R</sub> | I/O <sub>7R</sub>  | V <sub>ss</sub>    | С |

| D | ODR <sub>4</sub> | ODR <sub>2</sub> | BUSY <sub>R</sub> | $\overline{INT}_{R}$            | A <sub>10R</sub>                   | A <sub>12R</sub> <sup>(3)</sup>    | I/O <sub>13R</sub>  | I/O <sub>8R</sub>  | I/O <sub>5R</sub>  | I/O <sub>2R</sub>  | D |

| Е | V <sub>SS</sub>  | DNU              | ODR <sub>3</sub>  | $\overline{INT}_{L}$            | V <sub>SS</sub>                    | V <sub>SS</sub>                    | I/O <sub>4R</sub>   | V <sub>DDIOR</sub> | I/O <sub>1R</sub>  | V <sub>SS</sub>    | Е |

| F | SFEN             | ODR <sub>1</sub> | BUSYL             | A <sub>1L</sub>                 | $V_{DD}$                           | V <sub>SS</sub>                    | I/O <sub>3R</sub>   | I/O <sub>0R</sub>  | I/O <sub>15L</sub> | V <sub>DDIOL</sub> | F |

| G | ODR₀             | A <sub>2L</sub>  | A <sub>5L</sub>   | A <sub>12L</sub> <sup>(3)</sup> | $\overline{OE}_{L}$                | I/O <sub>3L</sub>                  | I/O <sub>11L</sub>  | I/O <sub>12L</sub> | I/O <sub>14L</sub> | I/O <sub>13L</sub> | G |

| н | A <sub>0L</sub>  | A <sub>4L</sub>  | A <sub>9L</sub>   | ĹΒL                             | CS∟                                | I/O <sub>1L</sub>                  | V <sub>DDIOL</sub>  | MSEL <sub>R</sub>  | MSEL∟              | I/O <sub>10L</sub> | н |

| J | A <sub>3L</sub>  | A <sub>7L</sub>  | A <sub>10L</sub>  | IRR <sub>0</sub> <sup>(2)</sup> | $V_{DD}$                           | V <sub>SS</sub>                    | I/O <sub>4L</sub>   | I/O <sub>6L</sub>  | I/O <sub>8L</sub>  | I/O <sub>9L</sub>  | J |

| K | A <sub>6L</sub>  | A <sub>8L</sub>  | A <sub>11L</sub>  | $\overline{UB}_{L}$             | $\overline{\text{ADV}}_{\text{L}}$ | $\overline{WE}_{L}$                | I/O <sub>0L</sub>   | I/O <sub>2L</sub>  | I/O <sub>5L</sub>  | I/O <sub>7L</sub>  | K |

|   | 1                | 2                | 3                 | 4                               | 5                                  | 6                                  | 7                   | 8                  | 9                  | 10                 |   |

|   |                  |                  |                   |                                 |                                    |                                    |                     |                    | 71                 | 146 drw 02         |   |

NOTES:-

1. This pin is A13R for IDT70P269.

2. This pin is A13L for IDT70P269.

3. This pin is DNU for IDT70P249.

4. DNU pins are "do not use". No trace or power component can be connected to these pins.

Fabricated using IDT's CMOS high-performance technology, these devices typically operate on only 27mW of power.

The IDT70P269/259/249 is packaged in a 100 ball 0.5mm-pitch Ball Grid Array. The package is a 1mm thick and designed to fit in wireless handset applications.

## Pin Names

| Chip Select (Input)<br>Read/Write Enable (Input)<br>Output Enable (Input) |

|---------------------------------------------------------------------------|

| Output Enable (Input)                                                     |

|                                                                           |

|                                                                           |

| Address (Input)                                                           |

| Mode Select (Input)                                                       |

| Address/Data (Input/Output)                                               |

| Address Latch Enable (Input)                                              |

| Upper Byte Enable (Input)                                                 |

| Lower Byte Enable (Input)                                                 |

| Interrupt Flag (Output)                                                   |

| Busy Flag (Output)                                                        |

| Special Function Enable (Input)                                           |

| Input Read Register (Inputs)                                              |

| Output Drive Register (Outputs)                                           |

| Core Power Supply (Input)                                                 |

| Ground (Input)                                                            |

| Left Port Power Supply (Input)                                            |

| Right Port Power Supply (Input)                                           |

|                                                                           |

#### NOTES:

1. A13 - A0 for IDT70P269; A12 - A0 for IDT70P259; A11 - A0 for IDT70P249. 2. MSEL = 0 for Standard SRAM operation, MSEL = 1 for Address/Data Mux (ADM) operation.

3. ADV is only used when the port is in ADM mode.

4. IRRo is A13L and IRR1 is A13R for 70P269.

## Truth Table I: ADM Interface Read/Write Control

|       |           | Inp | outs |    |    | Outputs                                        |                                  |

|-------|-----------|-----|------|----|----|------------------------------------------------|----------------------------------|

| ADV   | <u>cs</u> | WE  | ŌĒ   | ŪB | ΓB | I/O0 - I/O15                                   | Mode                             |

| х     | Н         | Х   | Х    | х  | Х  | High-Z                                         | Deselected/Power Down            |

| х     | Х         | Х   | Н    | х  | Х  | High-Z                                         | Output Disable                   |

| Х     | Х         | Х   | Х    | Н  | Н  | High-Z                                         | Upper and Lower Bytes Deselected |

| Pulse | L         | Н   | L    | L  | L  | DATAOUT (I/O0 - I/O15)                         | Read Upper and Lower Bytes       |

| Pulse | L         | Н   | L    | Н  | L  | DATAout (I/O0 - I/O7)<br>High-Z (I/O8 - I/O15) | Read Lower Byte Only             |

| Pulse | L         | Н   | L    | L  | Н  | High-Z (I/O0 - I/O7)<br>DATAout (I/O8 - I/O15) | Read Upper Byte Only             |

| Pulse | L         | L   | Х    | L  | L  | DATAIN (I/O0 - I/O15)                          | Write Upper and Lower Bytes      |

| Pulse | L         | L   | х    | Н  | L  | DATAIN (I/O0 - I/O7)<br>High-Z (I/O8 - I/O15)  | Write Lower Byte Only            |

| Pulse | L         | L   | х    | L  | Н  | High-Z (I/O₀ - I/O⁊)<br>DATAıN (I/Oଃ - I/O15)  | Write Upper Byte Only            |

7146 tbl 02a

# Truth Table II: Standard SRAM Interface Read/Write Control

|    |    | Inputs |    |    | Outputs                                        |                                  |

|----|----|--------|----|----|------------------------------------------------|----------------------------------|

| CS | WE | ŌĒ     | ŪB | LB | <b>I/O</b> 0 - <b>I/O</b> 15                   | Mode                             |

| Н  | Х  | х      | Х  | Х  | High-Z                                         | Deselected/Power Down            |

| х  | Х  | Н      | Х  | Х  | High-Z                                         | Output Disable                   |

| х  | Х  | х      | Н  | Н  | High-Z                                         | Upper and Lower Bytes Deselected |

| L  | Н  | L      | L  | L  | DATAOUT (I/O0 - I/O15)                         | Read Upper and Lower Bytes       |

| L  | Н  | L      | Н  | L  | DATAout (I/O0 - I/O7)<br>High-Z (I/O8 - I/O15) | Read Lower Byte Only             |

| L  | Н  | L      | L  | Н  | High-Z (I/O0 - I/O7)<br>DATAout (I/O8 - I/O15) | Read Upper Byte Only             |

| L  | L  | х      | L  | L  | DATAIN (1/O0 - 1/O15)                          | Write Upper and Lower Bytes      |

| L  | L  | х      | Н  | L  | DATAIN (I/O0 - I/O7)<br>High-Z (I/O8 - I/O15)  | Write Lower Byte Only            |

| L  | L  | х      | L  | Н  | High-Z (I/O₀ - I/O⁊)<br>DATAı∖ (I/Oଃ - I/O15)  | Write Upper Byte Only            |

7146 tbl 02b

## Absolute Maximum Ratings<sup>(1)</sup>

| Symbol               | Rating                                  | Commercial<br>& Industrial | Unit |

|----------------------|-----------------------------------------|----------------------------|------|

| Vterm <sup>(2)</sup> | Terminal Voltage with<br>Respect to GND | -0.5 to VDDIOX +0.5        | V    |

| TBIAS <sup>(3)</sup> | Temperature Under Bias                  | -55 to +125                | °C   |

| Тѕтҫ                 | Storage Temperature                     | -65 to +150                | °C   |

| ЛЛ                   | Junction Temperature                    | +150                       | °C   |

| Ιουτ                 | DC Output Current                       | 20                         | mA   |

#### NOTES:

7146 tbl 03

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VTERM must not exceed VDDIOX + 0.5V for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq$  20mA for the period over VTERM = VDDIOX + 0.5V.

3. Ambient Temperature under DC Bias. No AC Conditions. Chip Deselected.

## Capacitance

$(TA = +25^{\circ}C, f = 1.0MHz)$

| Symbol | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit        |

|--------|--------------------|---------------------------|------|-------------|

| Cin    | Input Capacitance  | VIN = 3dV                 | 9    | рF          |

| Соит   | Output Capacitance | Vout = 3dV                | 10   | pF          |

|        |                    |                           |      | 7146 tbl 05 |

NOTES:

1. This parameter is determined by device characterization but is not production tested.

3dV references the interpolated capacitance when the input and output signals switch from 0V to 3V or from 3V to 0V.

#### Industrial Temperature Range

# Maximum Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient<br>Temperature | GND | Vdd                                                               |

|------------|------------------------|-----|-------------------------------------------------------------------|

| Industrial | -40°C to +85°C         | 0V  | 1.8V <u>+</u> 100mV<br>2.5V <u>+</u> 100mV<br>3.0V <u>+</u> 300mV |

| NOTE       |                        |     | 7146 tbl 04                                                       |

NOTE :

1. This is the parameter TA. This is the "instant on" case temperature.

# DC Electrical Characteristics Over the Operating and Temperature and Supply Voltage Range(V<sub>DD</sub> = 1.8V)

|          | 70P269/259/249<br>Ind'l Only        |                   |                   |             |      |             |      |

|----------|-------------------------------------|-------------------|-------------------|-------------|------|-------------|------|

| Symbol   | Parameter                           | P1 I/O<br>Voltage | P2 I/O<br>Voltage | Min.        | Тур. | Max.        | Unit |

|          | Output High Voltage (Іон = -100 µA) | 1.8V (a           | ny port)          | Vddio - 0.2 | _    | _           | V    |

|          | Output High Voltage (Iон = -2 mA)   | 2.5V (a           | ny port)          | 2.0         | _    | _           | V    |

| Vон      | Output High Voltage (Iон = -2 mA)   | 3.0V (a           | ny port)          | 2.1         | _    | _           | V    |

|          | Output Low Voltage (Io∟ = 100 µA)   | 1.8V (a           | ny port)          |             | _    | 0.2         | V    |

|          | Output Low Voltage (Io∟ = 2 mA)     | 2.5V (a           | ny port)          |             | _    | 0.4         | V    |

| Vol      | Output Low Voltage (Io∟ = 2 mA)     | 3.0V (a           | ny port)          |             | _    | 0.4         | V    |

|          |                                     | 1.8V (a           | ny port)          |             | _    | 0.2         | V    |

|          |                                     | 2.5V (a           | ny port)          |             |      | 0.2         | V    |

| Vol ODR  | ODR Output Low Voltage (IoL = 8 mA) | 3.0V (a           | ny port)          |             |      | 0.2         | V    |

|          |                                     | 1.8V (a           | ny port)          | 1.2         |      | VDDIO + 0.2 | V    |

|          |                                     | 2.5V (a           | ny port)          | 1.7         |      | VDDIO+ 0.3  | V    |

| Viн      | Input High Voltage                  | 3.0V (a           | ny port)          | 2.0         | _    | VDDIO + 0.2 | V    |

|          |                                     | 1.8V (a           | ny port)          | -0.2        | _    | 0.4         | V    |

|          |                                     | 2.5V (a           | ny port)          | -0.3        |      | 0.6         | V    |

| VIL      | Input Low Voltage                   | 3.0V (a           | ny port)          | -0.2        |      | 0.7         | V    |

|          |                                     | 1.8V              | 1.8V              | -1          |      | 1           |      |

|          |                                     | 2.5V              | 2.5V              | -1          | _    | 1           |      |

| loz      | Output Leakage Current              | 3.0V              | 3.0V              | -1          |      | 1           | μA   |

|          |                                     | 1.8V              | 1.8V              | -1          | _    | 1           |      |

|          | ODR Output Leakage Current          | 2.5V              | 2.5V              | -1          |      | 1           |      |

| ICEX ODR | Vout = VDDIO                        | 3.0V              | 3.0V              | -1          | _    | 1           | μA   |

|          |                                     | 1.8V              | 1.8V              | -1          | —    | 1           | ]    |

|          |                                     | 2.5V              | 2.5V              | -1          | _    | 1           |      |

| lix      | Input Leakage Current               | 3.0V              | 3.0V              | -1          | _    | 1           | μA   |

7146 tbl 06

# DC Electrical Characteristics Over the Operating and Temperature and Supply Voltage Range(VDD = 2.5V)

|          |                                            |                   |                   |      |      | /259/249<br>Only |      |

|----------|--------------------------------------------|-------------------|-------------------|------|------|------------------|------|

| Symbol   | Parameter                                  | P1 I/O<br>Voltage | P2 I/O<br>Voltage | Min. | Тур. | Max.             | Unit |

|          | Output High Voltage (Iон = -2 mA)          | 2.5V (a           | ny port)          | 2.0  | —    |                  | V    |

| Vон      | Output High Voltage (Iон = -2 mA)          | 3.0V (a           | ny port)          | 2.1  | —    |                  | V    |

|          | Output Low Voltage (Io∟ = 2 mA)            | 2.5V (a           | ny port)          | _    | —    | 0.4              | V    |

| Vol      | Output Low Voltage (Io∟ = 2 mA)            | 3.0V (a           | ny port)          | _    | _    | 0.4              | V    |

|          |                                            | 2.5V (a           | ny port)          | _    | _    | 0.2              | V    |

| Vol ODR  | ODR Output Low Voltage (IoL = 8 mA)        | 3.0V (a           | ny port)          |      |      | 0.2              | V    |

|          |                                            | 2.5V (a           | ny port)          | 1.7  |      | VDDIO+ 0.3       | V    |

| Viн      | Input High Voltage                         | 3.0V (a           | ny port)          | 2.0  |      | VDDIO + 0.2      | V    |

|          |                                            | 2.5V (a           | ny port)          | -0.3 |      | 0.6              | V    |

| VIL      | Input Low Voltage                          | 3.0V (a           | ny port)          | -0.2 |      | 0.7              | V    |

|          |                                            | 2.5V              | 2.5V              | -1   | _    | 1                |      |

| loz      | Output Leakage Current                     | 3.0V              | 3.0V              | -1   | —    | 1                | μA   |

|          |                                            | 2.5V              | 2.5V              | -1   | —    | 1                |      |

| ICEX ODR | ODR Output Leakage Current<br>Vout = Vodio | 3.0V              | 3.0V              | -1   |      | 1                | μΑ   |

|          |                                            | 2.5V              | 2.5V              | -1   | —    | 1                |      |

| lix      | Input Leakage Current                      | 3.0V              | 3.0V              | -1   |      | 1                | μA   |

7146 tbl 07

# DC Electrical Characteristics Over the Operating and Temperature and Supply Voltage Range( $V_{DD} = 3.0V$ )

|          |                                            |                   |                   |      | 70P269/2<br>Ind'l ( |             |      |

|----------|--------------------------------------------|-------------------|-------------------|------|---------------------|-------------|------|

| Symbol   | Parameter                                  | P1 I/O<br>Voltage | P2 I/O<br>Voltage | Min. | Тур.                | Max.        | Unit |

| Vон      | Output High Voltage (Iон = -2 mA)          | 3.0V (a           | ny port)          | 2.1  | _                   |             | V    |

| Vol      | Output Low Voltage (IoL = 2 mA)            | 3.0V (a           | ny port)          | _    | _                   | 0.4         | V    |

| Vol ODR  | ODR Output Low Voltage (IoL = 8 mA)        | 3.0V (a           | ny port)          | _    | _                   | 0.2         | V    |

| Viн      | Input High Voltage                         | 3.0V (a           | ny port)          | 2.0  | _                   | VDDIO + 0.2 | V    |

| VIL      | Input Low Voltage                          | 3.0V (a           | ny port)          | -0.2 | _                   | 0.7         | V    |

| loz      | Output Leakage Current                     | 3.0V              | 3.0V              | -1   |                     | 1           | μA   |

| ICEX ODR | ODR Output Leakage Current<br>Vout = VDDIO | 3.0V              | 3.0V              | -1   |                     | 1           | μA   |

| lix      | Input Leakage Current                      | 3.0V              | 3.0V              | -1   |                     | 1           | μA   |

7146 tbl 08

# DC Electrical Characteristics Over the Operating and Temperature and Supply Voltage Range

|        |                                                           |                                                                                                                                     |      |      | 70P269/<br>Ind'l |      |      |         |

|--------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|------------------|------|------|---------|

|        |                                                           |                                                                                                                                     |      | 65   | ns               | 90   | ns   |         |

| Symbol | Parameter                                                 | Test Condition <sup>(1)</sup>                                                                                                       | VDD  | Тур. | Мах.             | Тур. | Max. | Uni     |

|        |                                                           |                                                                                                                                     | 1.8V | 25   | 40               | 15   | 25   |         |

| IDD    | Dynamic Operating Current                                 | $V_{DD} = M_{AX}, I_{OUT} = 0mA$                                                                                                    | 2.5V | 39   | 55               | 28   | 40   |         |

|        |                                                           |                                                                                                                                     | 3.0V | 49   | 70               | 42   | 60   | mA      |

|        |                                                           | $\overline{\text{CS}}_{\text{R}}$ and $\overline{\text{CS}}_{\text{L}} \ge \text{VDDIO} - 0.2\text{V}$ ,                            | 1.8V | 2    | 6                | 2    | 6    |         |

| ISB1   | Standby Current (Both Ports<br>Inactive)                  | MSELL and MSELR $\leq$ 0.2V<br>or $\geq$ VDDIO - 0.2V,                                                                              | 2.5V | 6    | 8                | 6    | 8    |         |

|        | ,                                                         | f = fMAX                                                                                                                            | 3.0V | 7    | 10               | 7    | 10   | μA      |

|        |                                                           |                                                                                                                                     | 1.8V | 8.5  | 18               | 8.5  | 14   |         |

| ISB2   | Standby Current (One Port<br>Active, One Port Inactive)   | $\overline{\text{CS}}_{\text{R}}$ or $\overline{\text{CS}}_{\text{L}} \ge \text{V}_{\text{DDIO}} - 0.2\text{V}$ ,<br>f = fmax       | 2.5V | 21   | 30               | 18   | 25   |         |

|        | ····, · · · · · · · · · · · · · · · · ·                   |                                                                                                                                     | 3.0V | 28   | 40               | 25   | 35   | mA      |

|        | Full Standby Current (Deth                                | $\overline{\text{CS}}_{\text{R}}$ and $\overline{\text{CS}}_{\text{L}} \ge \text{VDDIO} - 0.2\text{V}$ ,                            | 1.8V | 2    | 6                | 2    | 6    |         |

| ISB3   | Full Standby Current (Both<br>Ports Inactive - CMOS Level | MSELL and MSELR $\leq 0.2V$<br>or $\geq VDDIO - 0.2V$ ,                                                                             | 2.5V | 4    | 6                | 4    | 6    |         |

|        | Inputs)                                                   | f = 0                                                                                                                               | 3.0V | 6    | 8                | 6    | 8    | μA      |

|        | Standby Current (One Det                                  |                                                                                                                                     | 1.8V | 8.5  | 18               | 8.5  | 14   |         |

| ISB4   | Standby Current (One Port<br>Active, One Port Inactive -  | $\overline{\text{CS}}_{\text{L}} \text{ or } \overline{\text{CS}}_{\text{R}} \ge \text{V}_{\text{DDIO}} - 0.2\text{V},$<br>f = fmax | 2.5V | 21   | 30               | 18   | 25   |         |

|        | CMOS Level Inputs)                                        |                                                                                                                                     | 3.0V | 28   | 40               | 25   | 35   | mA      |

| NTC .  | -                                                         | -                                                                                                                                   |      | -    | -                |      | - 7  | 146 tbl |

#### NOTE :

1. fMAX = 1/tRC = All inputs cycling at f = 1/tRC (except output enable). f=0 means no address or control lines change. This applied only to inputs at CMOS level standby ISB3.

| Low Power 16K/8K/4K x 16 Dua  | al-Port Static RAM                  |  |  |  |

|-------------------------------|-------------------------------------|--|--|--|

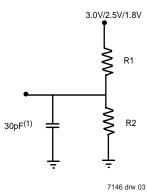

| AC Test Conditions            |                                     |  |  |  |

| Input Pulse Levels            | GND to 3.0V/GND to 2.5V/GND to 1.8V |  |  |  |

| Input Rise/Fall Times         | Input Rise/Fall Times 3ns Max.      |  |  |  |

| Input Timing Reference Levels | 1.5V/1.25V/0.9V                     |  |  |  |

| Output Reference Levels       | 1.5V/1.25V/0.9V                     |  |  |  |

| Output Load                   | Figure 1                            |  |  |  |

|                               | 7146 tbl 10                         |  |  |  |

IDT70P269/259/249L

| _ |    | 3.0V/2.5V | 1.8V        |

|---|----|-----------|-------------|

|   | R1 | 1022Ω     | 13500Ω      |

| ĺ | R2 | 729Ω      | 10800Ω      |

|   |    |           | 7146 tbl 11 |

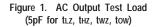

Timing of Power-Up Power-Down

7146 drw 04

8

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup>

| -                    |                                                                      |      |      |      |      |      |

|----------------------|----------------------------------------------------------------------|------|------|------|------|------|

|                      |                                                                      | 65   | ns   | 90   | ns   |      |

| Symbol               | Parameter                                                            | Min. | Мах. | Min. | Max. | Unit |

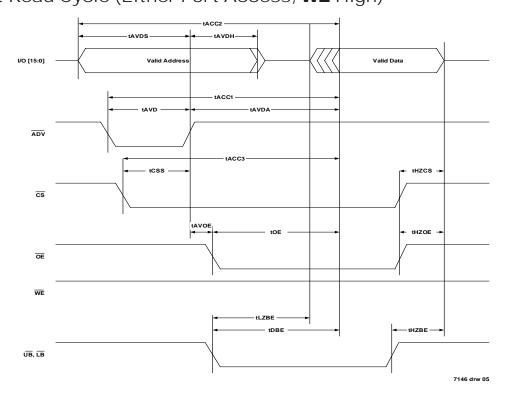

| ADM Po               | rt Read Cycle <sup>(2)</sup>                                         |      |      | -    |      |      |

| tRC                  | Read Cycle Time                                                      | 65   |      | 90   |      | ns   |

| tacc1                | Random Access ADV Low to Data Valid                                  |      | 65   |      | 90   | ns   |

| tacc2                | Random Access Address to Data Valid                                  |      | 65   |      | 90   | ns   |

| tacc3                | Random Access $\overline{CS}$ to Data Valid                          |      | 65   |      | 90   | ns   |

| tavda                | Random Access ADV High to Data Valid                                 |      | 35   |      | 50   | ns   |

| tavd                 | ADV Low Pulse                                                        | 15   |      | 20   |      | ns   |

| tavds                | Address Set-up to $\overline{\text{ADV}}$ Rising Edge                | 15   |      | 20   |      | ns   |

| tavdh                | Address Hold from $\overline{\text{ADV}}$ Rising Edge                | 3    |      | 5    |      | ns   |

| tcss                 | $\overline{\text{CS}}$ Set-up to $\overline{\text{ADV}}$ Rising Edge | 7    |      | 10   |      | ns   |

| toe                  | OE Low to Data Valid                                                 | —    | 35   |      | 50   | ns   |

| tlzoe <sup>(3)</sup> | OE Low to I/O Low-Z                                                  | 3    |      | 5    |      | ns   |

| thzoe <sup>(3)</sup> | OE High to I/O High-Z                                                |      | 15   |      | 25   | ns   |

| tHZCS <sup>(3)</sup> | CS High to I/O High-Z                                                |      | 15   |      | 25   | ns   |

| <b>t</b> DBE         | UB/LB Low to I/O Valid                                               |      | 35   |      | 50   | ns   |

| tlzbe <sup>(3)</sup> | UB/LB Low to I/O Low-Z                                               | 3    |      | 5    |      | ns   |

| tHZBE <sup>(3)</sup> | UB/LB High to I/O High-Z                                             |      | 15   |      | 25   | ns   |

| tavoe                | ADV High to OE Low                                                   | 0    |      | 0    |      | ns   |

| tPU                  | Chip Enable to Power Up Time                                         | 0    |      | 0    |      | ns   |

| tPD                  | Chip Disable to Power Down Time                                      |      | 65   |      | 90   | ns   |

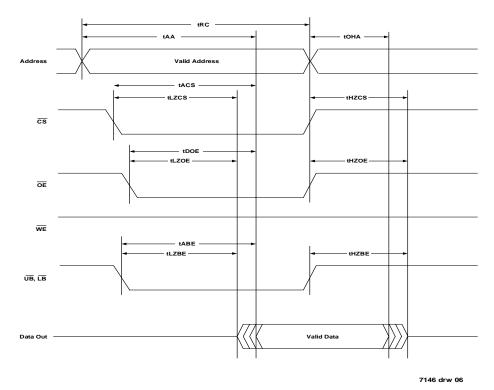

| Standard             | I Port Read Cycle <sup>(4)</sup>                                     |      |      |      |      |      |

| trc                  | Read Cycle Time                                                      | 40   |      | 60   |      | ns   |

| taa                  | Address to Data Valid                                                |      | 40   |      | 60   | ns   |

| tона                 | Output Hold from Address Change                                      | 5    |      | 5    |      | ns   |

| tacs                 | CS to Data Valid                                                     |      | 40   |      | 60   | ns   |

| <b>t</b> DOE         | OE Low to Data Valid                                                 |      | 25   |      | 35   | ns   |

| tlzoe <sup>(3)</sup> | OE Low to Data Low-Z                                                 | 5    |      | 5    |      | ns   |

| thzoe <sup>(3)</sup> | OE High to Data High-Z                                               |      | 10   |      | 30   | ns   |

| tLZCS <sup>(3)</sup> | CS Low to Data Low-Z                                                 | 5    |      | 5    |      | ns   |

| tHZCS <sup>(3)</sup> | CS Low to Data High-Z                                                |      | 10   |      | 30   | ns   |

| tlzbe <sup>(3)</sup> | UB/LB Low to Data Low-Z                                              | 5    |      | 5    |      | ns   |

| thzbe <sup>(3)</sup> | UB/LB High to Data High-Z                                            |      | 10   |      | 30   | ns   |

| tabe                 | UB/LB Access Time                                                    |      | 40   |      | 60   | ns   |

7146 tbl 12

NOTES: 1. VDD = 1.8V

2. ADM port timing applies to the left or right port when configured to ADM mode.

This parameter is guaranteed by design and is not tested.

Standard SRAM port timing applies to the left or right port when configured to standard SRAM mode.

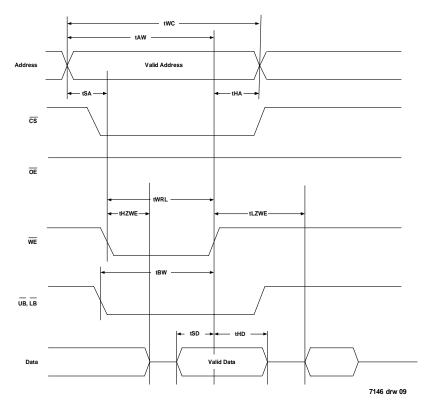

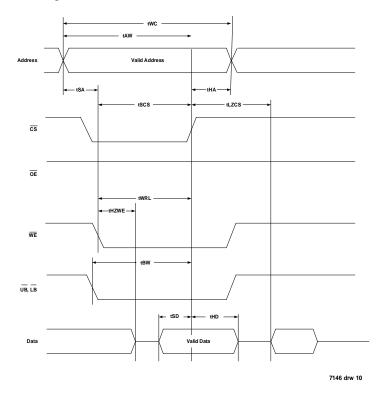

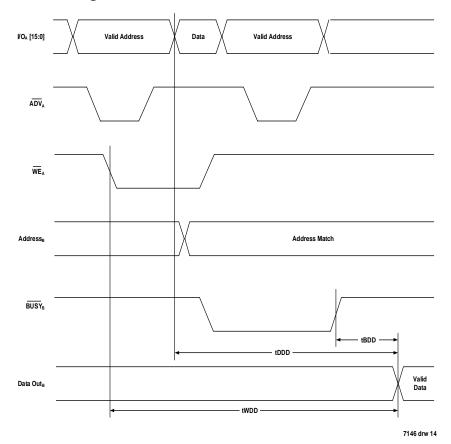

Standard Port Read Cycle (Right Port Access, WE High)

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup>

|                      |                                   |      | 70P269/259/249 |      |      |      |  |

|----------------------|-----------------------------------|------|----------------|------|------|------|--|

|                      |                                   | 65   | ns             | 90   |      |      |  |

| Symbol               | Parameter                         | Min. | Max.           | Min. | Max. | Unit |  |

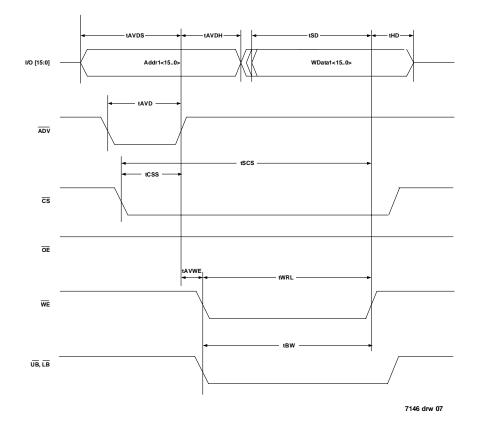

| ADM Por              | rt Write Cycle <sup>(2)</sup>     |      |                |      |      |      |  |

| twc                  | Write Cycle Time                  | 65   |                | 90   |      | ns   |  |

| tscs                 | CS Low to Write End               | 65   |                | 90   |      | ns   |  |

| tavd                 | ADV Low Pulse                     | 15   |                | 20   |      | ns   |  |

| tavds                | Address Set-up to ADV Rising Edge | 15   |                | 20   |      | ns   |  |

| tavdh                | Address Hold from ADV Rising Edge | 3    |                | 5    |      | ns   |  |

| tcss                 | CS Set-up to ADV Rising Edge      | 7    |                | 10   |      | ns   |  |

| twrl                 | WE Pulse Width                    | 28   |                | 45   |      | ns   |  |

| tвw                  | UB/LB Low to Write End            | 28   |                | 45   |      | ns   |  |

| tsd                  | Data Set-up to Write End          | 20   |                | 30   |      | ns   |  |

| thd                  | Data Hold from Write End          | 0    |                | 0    |      | ns   |  |

| tlzwe <sup>(3)</sup> | WE High to I/O Low-Z              | 0    |                | 0    |      | ns   |  |

| tavwe                | ADV High to WE Low                | 0    |                | 0    |      | ns   |  |

| twodr                | Write End to ODR Valid            |      | 40             |      | 60   | ns   |  |

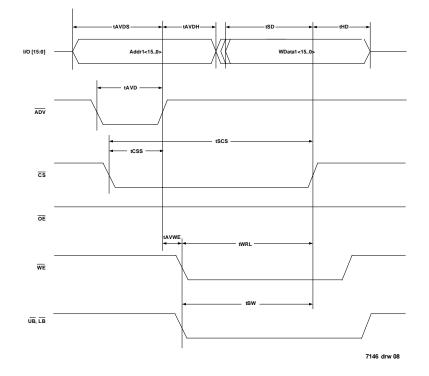

| Standard             | Port Write Cycle <sup>(4)</sup>   |      |                |      |      |      |  |

| twc                  | Write Cycle Time                  | 40   |                | 60   |      | ns   |  |

| tscs                 | CS Low to Write End               | 30   |                | 50   |      | ns   |  |

| taw                  | Address Valid to Write End        | 30   |                | 50   |      | ns   |  |

| tha                  | Address Hold to Write End         | 0    |                | 0    |      | ns   |  |

| tsa                  | Address Set-up to Write Start     | 0    |                | 0    |      | ns   |  |

| twrl                 | Write Pulse Width                 | 25   |                | 45   |      | ns   |  |

| tsd                  | Data Set-up to Write End          | 20   |                | 30   |      | ns   |  |

| thd                  | Data Hold from Write End          | 0    |                | 0    |      | ns   |  |

| tHZWE <sup>(3)</sup> | WE Low to Data High-Z             |      | 15             |      | 25   | ns   |  |

| tlzwe <sup>(3)</sup> | WE High to Data Low-Z             | 0    |                | 0    |      | ns   |  |

| twodr                | Write End to ODR Valid            |      | 40             |      | 60   | ns   |  |

NOTES: 1. VDD = 1.8V

2. ADM port timing applies to the left or right port when configured to ADM mode.

3. This parameter is guaranteed by design and is not tested.

4. Standard SRAM port timing applies to the left or right port when configured to standard SRAM mode.

ADM Port Write Cycle (Either Port Access, WE Controlled, OE High)

ADM Port Write Cycle (Either Port Access, CS Controlled, OE High)

# Standard Port Write Cycle (Either Port Access, WE Controlled)

Standard Port Write Cycle (Either Port Access, **CS** Controlled)

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup>

|                    |                                     | 65   | ns   | 90   | 1    |            |

|--------------------|-------------------------------------|------|------|------|------|------------|

| Symbol             | Parameter                           | Min. | Max. | Min. | Max. | Unit       |

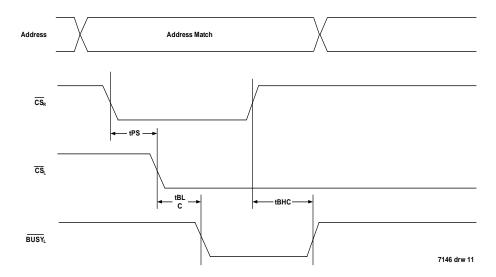

| Arbitratio         | on Timing                           |      |      |      |      |            |

| tbla               | BUSY Low from Address Match         |      | 30   |      | 50   | ns         |

| tвна               | BUSY High from Address Match        |      | 30   |      | 50   | ns         |

| <b>t</b> BLC       | BUSY Low from CS Low                |      | 30   |      | 50   | ns         |

| tвнс               | BUSY High from CS High              |      | 30   |      | 50   | ns         |

| tps <sup>(2)</sup> | Port Set-up Priority                | 5    |      | 5    |      | ns         |

| tBDD               | BUSY High to Data Valid             |      | 30   |      | 50   | ns         |

| twdd               | Write Pulse to Data Delay           |      | 55   |      | 85   | ns         |

| todd               | Write Data Valid to Read Data Valid |      | 45   |      | 70   | ns         |

|                    |                                     |      |      |      |      | 7146 tbl 1 |

NOTES:

1. VDD = 1.8V.

2. Add 2 ns to this parameter if VDD and VDDIOR are <1.8V, and VDDIOL is >2.5V at temperature <0°C.

# Arbitration Timing

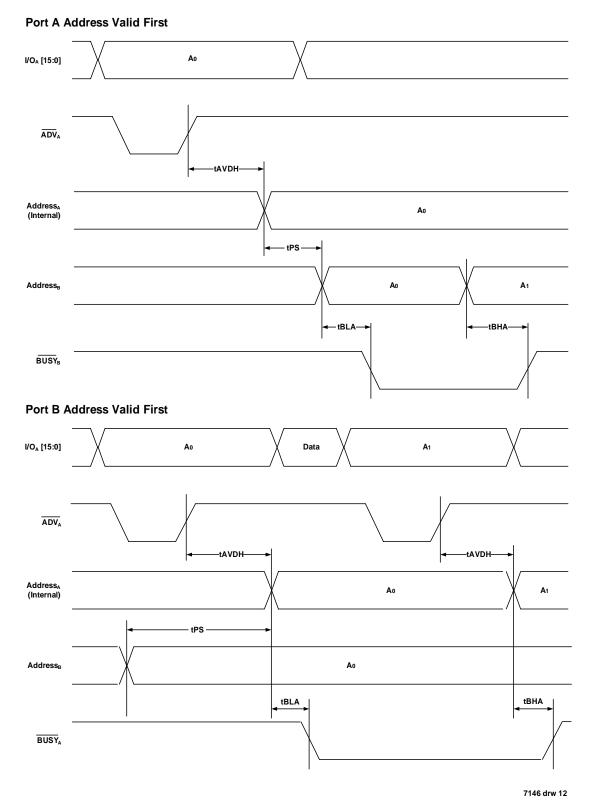

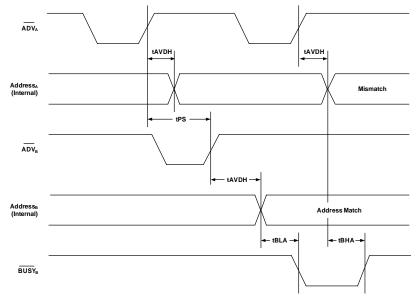

# Arbitration Timing (Address Controlled with Port A ADM and Port B STD Configuration)

## Arbitration Timing

(Address Controlled with Port A ADM and Port B ADM Configuration)

7146 drw 13

## Read with BUSY Timing

#### NOTES:

- 1. twod is measured from the time WE goes low on Port A to the beginning of valid data on Port B whether the ports are in ADM or Standard mode.

- 2. tDDD is measured from the end of valid address on Port A to the beginning of valid data on Port B whether the ports are in ADM or Standard mode.

- 3. tBDD is measured from the time BUSY goes high on Port B to the beginning of valid data on Port B whether the ports are in ADM or Standard mode.

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup>

|           |                |      | 70P269/259/249 |       |      |             |

|-----------|----------------|------|----------------|-------|------|-------------|

|           |                | 65   | ns             | 90 ns |      |             |

| Symbol    | Parameter      | Min. | Max.           | Min.  | Max. | Unit        |

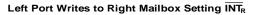

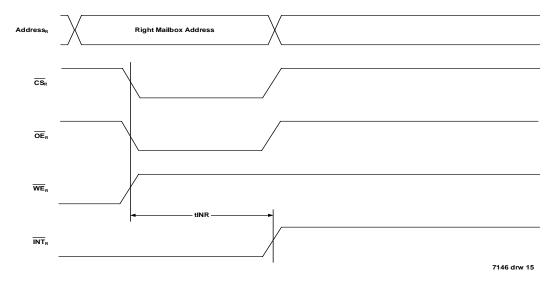

| Interrupt | Timing         |      |                |       |      |             |

| tins      | INT Set Time   |      | 35             |       | 55   | ns          |

| tinr      | INT Reset Time |      | 35             |       | 55   | ns          |

|           |                |      |                |       |      | 7146 tbl 15 |

NOTE: 1. VDD = 1.8V

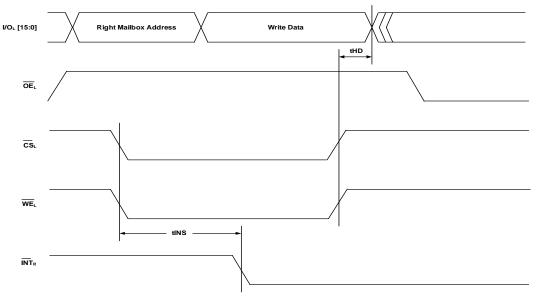

## Interrupt Timing

Right Port Reads Right Mailbox Clearing  $\overline{\text{INT}}_{R}$

# Truth Table III — Interrupt Flag<sup>(1)</sup>

|    |           | Left Port |                     |      | Right Port |           |             |                     |              |                       |

|----|-----------|-----------|---------------------|------|------------|-----------|-------------|---------------------|--------------|-----------------------|

| WE | <u>cs</u> |           | A13L-A0L            | ĪNTL | WE         | <u>cs</u> | <b>OE</b> R | A13R-A0R            | <b>INT</b> R | Function              |

| L  | L         | Х         | 3FFF <sup>(2)</sup> | Х    | Х          | Х         | Х           | Х                   | L            | Set Right INTR Flag   |

| Х  | Х         | Х         | Х                   | Х    | Х          | L         | L           | 3FFF <sup>(2)</sup> | Н            | Reset Right INTR Flag |

| Х  | Х         | Х         | Х                   | L    | L          | L         | Х           | 3FFE <sup>(3)</sup> | Х            | Set Left INT∟ Flag    |

| Х  | L         | L         | 3FFE <sup>(3)</sup> | Н    | Х          | Х         | Х           | Х                   | Х            | Reset Left INT∟ Flag  |

NOTES:

1. Assumes  $\overline{\text{BUSY}}_{L} = \overline{\text{BUSY}}_{R} = V_{IH}$ .

2. 3FFF for 70P269, 1FFF for 70P259, FFF for 70P249.

3. 3FFE for 70P269, 1FFE for 70P259, FFE for 70P249.

|            | In | puts                             | Out   | puts  |                              |  |  |  |  |

|------------|----|----------------------------------|-------|-------|------------------------------|--|--|--|--|

| Շs⊾        |    | Address Match<br>Left/Right Port | BUSY∟ | BUSYR | Function                     |  |  |  |  |

| Х          | Х  | NO MATCH                         | Н     | Н     | Normal                       |  |  |  |  |

| Н          | Х  | MATCH                            | Н     | Н     | Normal                       |  |  |  |  |

| Х          | Н  | MATCH                            | Н     | Н     | Normal                       |  |  |  |  |

| L          | L  | MATCH                            | (1)   | (1)   | Write Inhibit <sup>(2)</sup> |  |  |  |  |

| 7146 bl 17 |    |                                  |       |       |                              |  |  |  |  |

## Truth Table IV — Address BUSY Arbitration

#### NOTES:

1. L if the inputs to the opposite port were stable prior to the address and enable inputs of this port. H if the inputs to the opposite port became stable after the address and enable inputs of this port. If the input stable after the address and enable inputs of this port. If the input stable after the address and enable inputs of this port. If the input stable after the address and enable inputs of this port. If the input stable after the address and enable inputs of this port. If the input stable after the address and enable inputs of this port. If the input stable after the address and enable after the address after

Writes to the left port are internally ignored when BUSYL outputs are driving LOW regardless of actual logic level on the pin. Writes to the right port are internally ignored when BUSYR outputs are driving LOW regardless of actual logic level on the pin.

7146 tbl 16

#### SFEN CS WE ŌĒ ŪB LΒ ADDR I/O0-I/O1 I/O2-I/O15 Mode L<sup>(1)</sup> L<sup>(1)</sup> Н L Н L x0000 - Max VALID<sup>(1)</sup> VALID<sup>(1)</sup> Standard Memory Access VALID<sup>(2)</sup> VALID<sup>(4)</sup> Н Х x0000 IRR Read<sup>(3)</sup> L L L L 7146 tbl 18

# Truth Table V — Input Read Register Operation<sup>(3)</sup>

NOTES:

1.  $\overline{UB}$  or  $\overline{LB}$  = VIL. If  $\overline{LB}$  = VIL, then I/O0 - I/O7 are VALID. If  $\overline{UB}$  = VIL, then I/O8 - I/O15 are VALID.

2.  $\overline{LB}$  must be active ( $\overline{LB} = V_{IL}$ ) for these bits to be valid.

3.  $\overline{\text{SFEN}} = \text{ViL}$  to activate IRR reads.

4. Valid data bits from memory.

## Truth Table VI — Output Drive Register Operation<sup>(5)</sup>

| SFEN | Ē | R/₩ | ŌĒ               | ŪB               | ĽΒ               | ADDR        | I/O0-I/O4            | I/O5-I/O15           | Mode                       |

|------|---|-----|------------------|------------------|------------------|-------------|----------------------|----------------------|----------------------------|

| Н    | L | Н   | X <sup>(1)</sup> | L <sup>(2)</sup> | L <sup>(2)</sup> | x0000 - Max | VALID <sup>(2)</sup> | VALID <sup>(2)</sup> | Standard Memory Access     |

| L    | L | L   | Х                | Х                | L                | x0001       | VALID <sup>(3)</sup> | VALID <sup>(4)</sup> | ODR Write <sup>(4,5)</sup> |

| L    | L | Н   | L                | Х                | L                | x0001       | VALID <sup>(3)</sup> | VALID <sup>(6)</sup> | ODR Read <sup>(5)</sup>    |

|      |   |     |                  |                  |                  |             |                      |                      | 7146 tbl 19                |

NOTES:

1. Output enable must be low (OE = Vil) during reads for valid data to be output.

2.  $\overline{UB}$  or  $\overline{LB} = V_{1L}$ . If  $\overline{LB} = V_{1L}$ , then I/O0 - I/O7 are VALID. If  $\overline{UB} = V_{1L}$ , then I/O8 - I/O15 are VALID.

3.  $\overline{LB}$  must be active ( $\overline{LB} = V_{1L}$ ) for these bits to be valid.

4. During ODR writes data will also be written to the memory.

5.  $\overline{\text{SFEN}}$  = VIL to activate ODR reads and writes.

6. Valid data bits from memory.

#### Functional Description

The IDT70P269/259/249 are low-power CMOS 16K/8K/4K x 16 dual-port static RAMs. The two ports support user configurable standard SRAM or time-multiplexed address and data (ADM) interfaces. The two ports provide separate control, address, and I/O pins that permit independent, asynchronous read and write access to any memory location. The IDT70P269/259/249 has an automatic power-down feature controlled by  $\overline{CS}$ . The  $\overline{CS}$  controls on-chip power down circuitry that permits the respective port to go into a standby mode when not selected ( $\overline{CS}$  HIGH).

### Power Supply

The core voltage (V<sub>DD</sub>) can be 1.8V, 2.5V or 3.0V, as long as it is lower than or equal to the I/O voltage. Each port can operate on independent I/O voltages. This is determined by what is connected to the V<sub>DDIOL</sub> and V<sub>DDIOR</sub> pins. The supported I/O standards are 1.8V/2.5V LVCMOS and 3.0V LVTTL.

The IDT70P269/259/249 includes power supply isolation functionality which aids system power management. VDD, VDDIOR and VDDIOL can all be independently powered up/down which allows either port and/or the core to be powered down when not in use. If VDDIOX is powered down, but VDD remains powered up all inputs to the core will be forced to deasserted states at full swing DC values to minimize leakage current and active power consumption. If VDD is powered down but VDDIOX remain powered up, all outputs for the port(s) in question will remain in the state they were in prior to power down.

## ADM Interface Read/Write Operation

The description of this section is applicable to either port when configured in ADM mode.

Three control signals,  $\overline{ADV}$ ,  $\overline{WE}$ , and  $\overline{CS}$  are used to perform the read/ write operation. Address signals are first applied to the I/O bus along with  $\overline{CS}$  LOW. The addresses are loaded from the I/O bus in response to the rising edge of the Address Latch Enable ( $\overline{ADV}$ ) signal. It is necessary to meet the set-up (tavbs) and hold (tavbH) times given in the AC specifications with valid address information in order to properly latch the addresses.

Once the address signals are latched in, a read operation is issued when  $\overline{\text{WE}}$  stays HIGH. The I/O bus becomes HIGH-Z once the address signals meeting tavoh. The read data is driven on the I/O bus toe after the  $\overline{\text{OE}}$  is asserted LOW, and held until thzoe or thzcs after the rising edge of  $\overline{\text{OE}}$  or  $\overline{\text{CS}}$ , whichever comes first.

A write operation is issued when  $\overline{\text{WE}}$  is asserted LOW. The write data is applied to the I/O bus right after address meets the hold time (tavdh). And write data is written with the rising edge of either  $\overline{\text{WE}}$  or  $\overline{\text{CS}}$ , whichever comes first, and meets data set-up (tsd) and hold (thd) times.

A write operation is issued when  $\overline{WE}$  is asserted LOW. The write data is applied to the I/O bus right after address meets the hold time (tavDH). And write data is written with the rising edge of either  $\overline{WE}$  or  $\overline{CS}$ , whichever comes first, and meets data set-up (tsD) and hold (tHD) times.

## Standard SRAM Interface Read/ Write Operation

The description of this section is applicable to either port when configured to operate in Standard SRAM mode. Read/write operation with standard SRAM interface configuration is the same as the ADM port except addresses are presented on the address bus. Operation is controlled by  $\overline{CS}$ ,  $\overline{OE}$  and  $\overline{WE}$ . A read operation is issued when WE is asserted HIGH. A write operation is issued when  $\overline{WE}$  is asserted LOW. The I/O bus is the destination for read data and the source data for write data when the read operation is issued. However, write data needs to be driven to the I/O when the write operation is issued.

### Interrupts

If the user chooses the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag (INTL) is asserted when the right port writes to memory location 3FFE (HEX) (1FFE for IDT70P259 and FFE for IDT70P249), where a write is defined as the  $\overline{CS}=\overline{WE}=VIL$  per Truth Table III. The left port clears the interrupt by accessing address location 3FFE when  $\overline{CSR}=\overline{OER}=VIL$ ,  $\overline{WE}$ is a "don't care". Likewise, the right port interrupt flag (INTR) is asserted when the left port writes to memory location 3FFF (HEX) (1FFF for IDT70P259 and FFF for IDT70P249) and to clear the interrupt flag (INTR), the right port must read the memory location 3FFF. The message (16 bits) at 3FFE or 3FFF is user-defined, since it is an addressable SRAM location. If the interrupt function is not used, address locations 3FFE and 3FFF are not used as mail boxes, but as part of the random access memory. Refer to Truth Table III for the interrupt operation.

## **BusyLogic**

Busy Logic provides a hardware indication that both ports of the SRAM have accessed the same location at the same time. It also allows one of the two accesses to proceed and signals the other side that the SRAM is "busy". The BUSY pin can then be used to stall the access until the operation on the other side is completed. If a write operation has been attempted from the side that receives a BUSY indication, the write signal is gated internally to prevent the write from proceeding.

The use of BUSY logic is not required or desirable for all applications. In some cases it may be useful to logically OR the BUSY outputs together and use any BUSY indication as an interrupt source to flag the event of an illegal or illogical operation.

# Input Read Register

The Input Read Register (IRR) of the IDT70P269/259/249 captures the status of two external binary input devices connected to the Input Read pins (e.g. DIP switches). The contents of the IRR are read as a standard memory access to address x0000 from either port and the data is output via the standard I/Os (Truth Table V). During Input Register reads I/Oo - I/O1 are valid bits and I/O2 - I/O15 are read from the memory. Writes to address x0000 are normal memory operation. When SFEN = VIH, the IRR is inactive and address x0000 can be used as part of the main memory. The IRR inputs will be 1.8V/2.5V LVCMOS or 3.0V LVTTL, depending on the core voltage supply. Refer to Truth Table V for Input Read Register operation.

# **Output Drive Register**

The Output Drive Register (ODR) of the IDT70P269/259/249 determines the state of up to five external binary-state devices by providing a path to Vss for the external circuit. The five external devices supported by the ODR can operate at different voltages ( $1.5V \le V_{SUPPLY} \le 3.5V$ ), but the combined current of the devices must not exceed 40 mA (8mA IMAX for each external device). The status of the ODR bits is set using standard write accesses from either port to address x0001 with a "1" corresponding to "on" and a "0" corresponding to "off". The status of the ODR bits can also be read (without changing the status of the bits) via a standard read to address x0001. When  $\overline{SFEN} = V_{IL}$ , the ODR is active and address x0001 is not available for standard memory operations. When  $\overline{SFEN} = V_{IH}$ , the ODR is inactive and address x0001 can be used as part of the main memory. During reads and writes to the ODR I/O0 - I/O4 are valid bits and I/O5 -I/O15 will not affect the ODR function but they will read from or write to the memory. Refer to Truth Table VI for Output Drive Register operation.

7146 drw 16

# Datasheet Document History

10/16/08: Initial Datasheet

*CORPORATE HEADQUARTERS* 6024 Silver Creek Valley Road San Jose, CA 95138 *for SALES:* 800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com

*for Tech Support:* 408-284-2794 DualPortHelp@idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.