# ML610Q174 User's Manual

Issue Date: Nov. 8, 2013

#### **NOTES**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd. The content specified herein is subject to change for improvement without notice.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2013 LAPIS Semiconductor Co., Ltd.

FEUL610Q174-01

## **Preface**

This manual describes the operation of the hardware of the 8-bit microcontroller ML610Q174.

The following manuals are also available. Read them as necessary.

- nX-U8/100 Core Instruction Manual

Description on the basic architecture and the each instruction of the nX-U8/100 Core.

- MACU8 Assembler Package User's Manual Description on the method of operating the relocatable assembler, the librarian, and the object converter and also on the specifications of the assembler language.

- CCU8 User's Manual

Description on the method of operating the compiler.

- CCU8 Programming Guide

Description on the method of programming.

- CCU8 Language Reference

Description on the language specifications.

- DTU8 Debugger User's Manual Description on the method of operating the debugger DTU8.

- IDEU8 User's Manual Description on the integrated development environment IDEU8.

- uEASE User's Manual Description on the on-chip debug tool uEASE.

- uEASE connection Manual for ML610QXXX

Description about the connection between uEASE and ML610QXXX

- FWuEASE Flash Writer Host Program User's Manual Description on the Flash Writer host program.

FEUL610Q174-01 ii

# **Notation**

| Classification  | Notation                                                                                                 | Description                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ◆ Numeric value | xxh, xxH<br>xxb                                                                                          | Indicates a hexadecimal number. x: Any value in the range of 0 to F Indicates a binary number; "b" may be omitted. x: A value 0 or 1                                                                                 |

| ♦ Unit          | word, W byte, B nibble, N maga-, M kilo-, K kilo-, k milli-, m micro-, µ nano-, n second, s (lower case) | 1 word = 16 bits<br>1 byte = 8 bits<br>1 nibble = 4 bits<br>$10^6$<br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                              |

| ◆ Terminology   | "H" level, "1" level "L" level, "0" level                                                                | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics. Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |

### ♦ Register description

R/W: Indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

FEUL610Q174-01 iii

## **Table of Contents**

| Table of Contents                           |      |

|---------------------------------------------|------|

| Chapter 1                                   |      |

| 1. Overview                                 |      |

| 1.1 Features                                |      |

| 1.2 Configuration of Functional Blocks      |      |

| 1.2.1 Block Diagram of ML610Q174            |      |

| 1.3 Pins                                    |      |

| 1.3.1.1 Pin Layout of ML610Q174 QFP Package |      |

| 1.3.2 List of Pins                          |      |

| 1.3.3 Pin Description                       |      |

| 1.3.4 Termination of Unused Pins            |      |

| Chapter 2                                   |      |

|                                             | 2.1  |

| 2 CPU and Memory Space                      |      |

| 2.1 Overview                                |      |

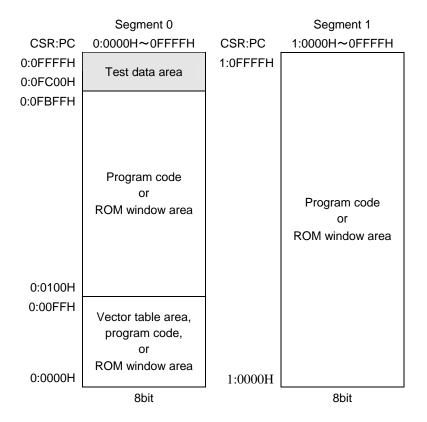

| 2.2 Program Memory Space                    |      |

| J -1                                        |      |

| E                                           |      |

| 2.5 Data Type                               |      |

| 2.6.1 List of Registers                     |      |

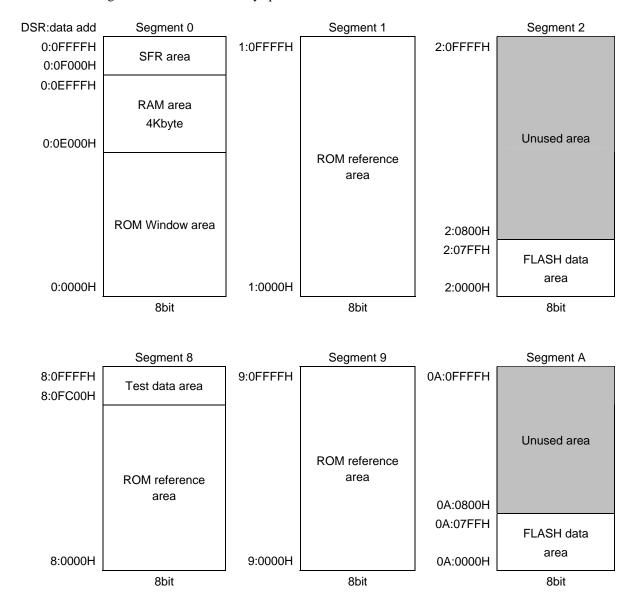

| 2.6.2 Data Segment Register (DSR)           |      |

| 2.0.2 Data Segment Register (DSR)           | 2 :  |

| Chapter 3                                   |      |

| •                                           |      |

| 3. Reset Function                           |      |

| 3.1 Overview                                |      |

| 3.1.1 Features                              |      |

| 3.1.2 Configuration                         |      |

| 3.1.3 List of Pin                           |      |

| 3.2 Description of Registers                |      |

| 3.2.1 List of Registers                     |      |

| 3.2.2 Reset Status Register (RSTAT)         |      |

| 3.3 Description of Operation                |      |

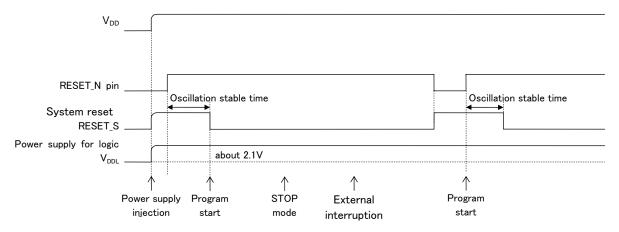

| 3.3.1 Operation of System Reset Mode        | 3-3  |

| Chapter 4                                   |      |

| 4. MCU Control Function                     |      |

| 4.1 Overview                                |      |

| 4.1.1 Features                              |      |

| 4.1.2 Configuration                         |      |

| 4.2 Description of Registers                |      |

| 4.2.1 List of Registers                     |      |

| 4.2.2 Stop Code Acceptor (STPACP)           |      |

| 4.2.3 Standby Control Register (SBYCON)     |      |

| 4.2.4 Block Control Register 0 (BLKCON0)    |      |

| 4.2.5 Block Control Register 2 (BLKCON2)    |      |

| 4.2.6 Block Control Register 4 (BLKCON4)    |      |

| 4.2.7 Block Control Register 6 (BLKCON6)    |      |

| 4.2.8 Block Control Register 7 (BLKCON7)    |      |

| 4.3 Description of Operation                |      |

| 4.3.1 Program Run Mode                      |      |

| 4 3 2 HALT Mode                             | 4-11 |

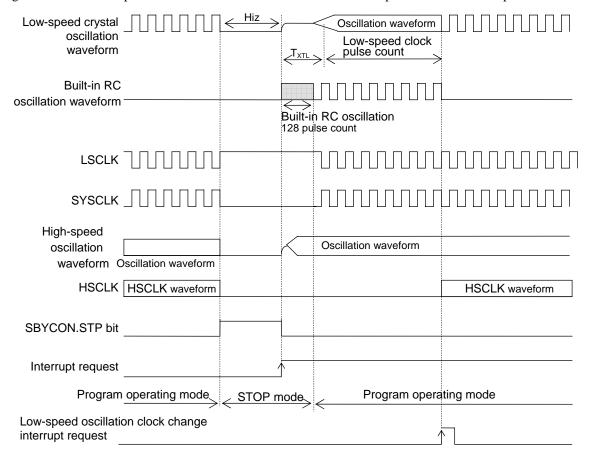

| 4.3.3.1 STOP Mode When CPU Operates with Low-Speed Clock                        |      |

|---------------------------------------------------------------------------------|------|

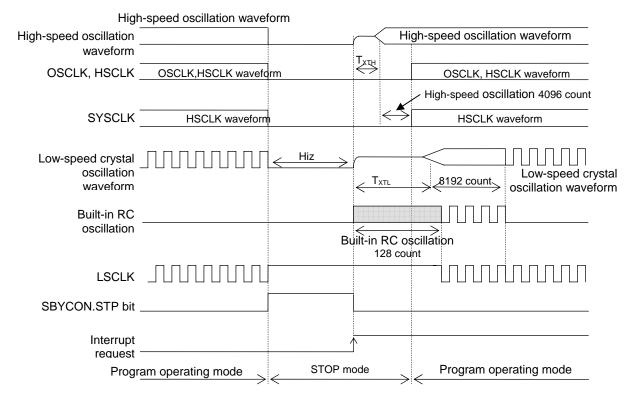

| 4.3.3.2 STOP Mode When CPU Operates with High-Speed Clock                       |      |

| 4.3.3.3 Note on Return Operation from STOP/HALT Mode                            |      |

| 4.3.4 Block control function                                                    | 4-15 |

| Chapter 5                                                                       |      |

|                                                                                 |      |

| 5. Interrupts (INTs)                                                            |      |

| 5.1 Overview                                                                    |      |

| 5.1.1 Features                                                                  |      |

| 5.2 Description of Registers                                                    |      |

| 5.2.1 List of Registers                                                         |      |

| 5.2.3 Interrupt Enable Register 1 (IE1)                                         |      |

| 5.2.4 Interrupt Enable Register 2 (IE2)                                         |      |

| 5.2.5 Interrupt Enable Register 3 (IE3)                                         |      |

| 5.2.6 Interrupt Enable Register 4 (IE4)                                         |      |

| 5.2.7 Interrupt Enable Register 5 (IE5)                                         |      |

| 5.2.8 Interrupt Enable Register 6 (IE6)                                         |      |

| 5.2.9 Interrupt Enable Register 7 (IE7)                                         |      |

| 5.2.10 Interrupt Request Register 0 (IRQ0)                                      |      |

| 5.2.11 Interrupt Request Register 1 (IRQ1)                                      |      |

| 5.2.12 Interrupt Request Register 2 (IRQ2)                                      |      |

| 5.2.13 Interrupt Request Register 3 (IRQ3)                                      |      |

| 5.2.14 Interrupt Request Register 4 (IRQ4)                                      | 5-15 |

| 5.2.15 Interrupt Request Register 5 (IRQ5)                                      | 5-16 |

| 5.2.16 Interrupt Request Register 6 (IRQ6)                                      | 5-17 |

| 5.2.17 Interrupt Request Register 7 (IRQ7)                                      |      |

| 5.3 Description of Operation                                                    |      |

| 5.3.1 Maskable Interrupt Processing                                             |      |

| 5.3.2 Non-Maskable Interrupt Processing                                         |      |

| 5.3.3 Software Interrupt Processing                                             |      |

| 5.3.4 Notes on Interrupt Routine                                                |      |

| 5.3.5 Interrupt Disable State                                                   | 5-25 |

| Chapter 6                                                                       |      |

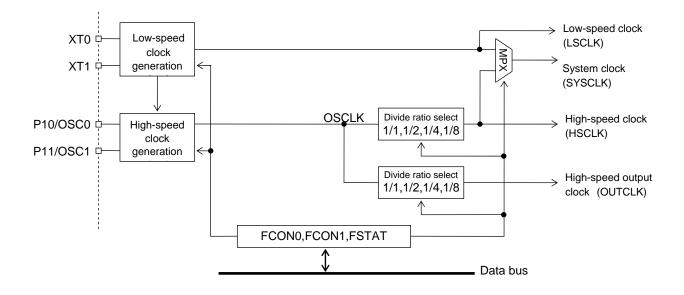

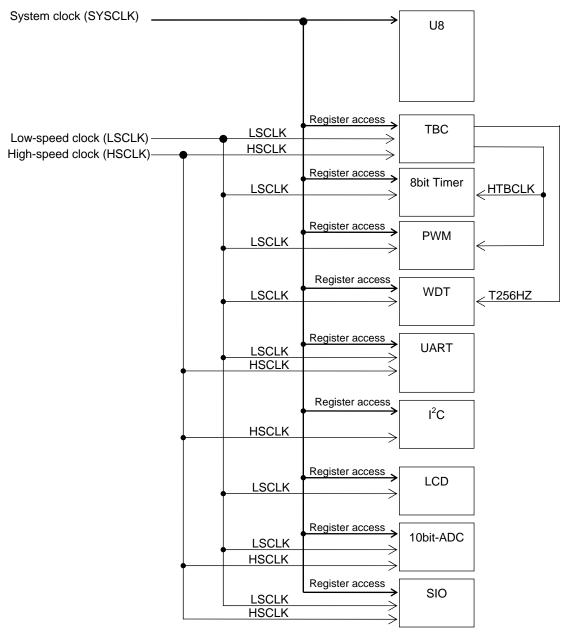

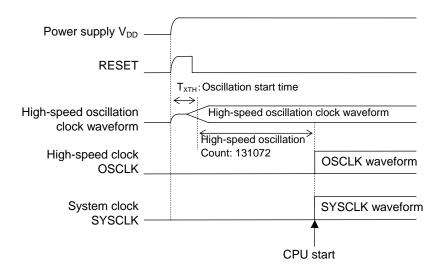

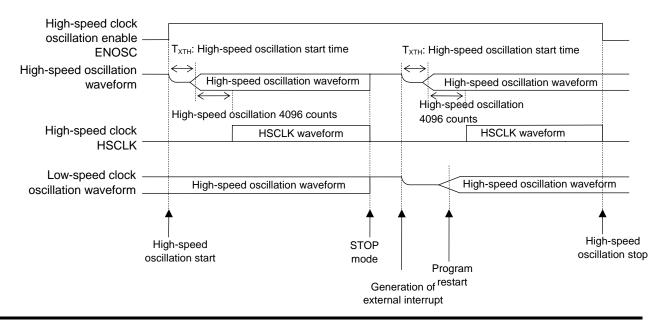

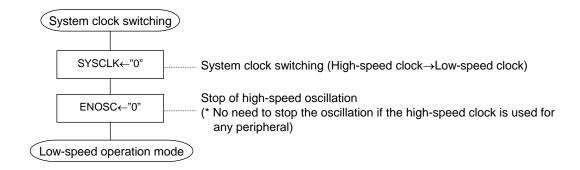

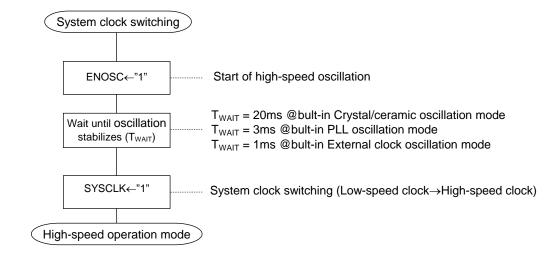

| 6. Clock Generation Circuit                                                     | 6-1  |

| 6.1 Overview                                                                    |      |

| 6.1.1 Features                                                                  | 6-1  |

| 6.1.2 Configuration                                                             |      |

| 6.1.3 List of Pins                                                              | 6-2  |

| 6.1.4 Clock Configuration                                                       | 6-2  |

| 6.2 Description of Registers                                                    | 6-3  |

| 6.2.1 List of Registers                                                         |      |

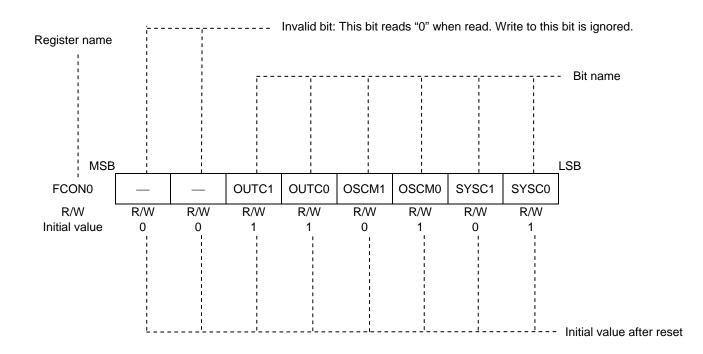

| 6.2.2 Frequency Control Register 0(FCON0)                                       |      |

| 6.2.3 Frequency Control Register 1 (FCON1)                                      |      |

| 6.2.4 Frequency Status Register (FSTAT)                                         |      |

| 6.3 Description of Operation                                                    |      |

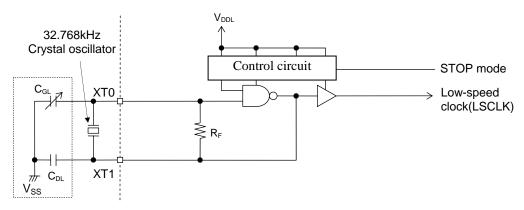

| 6.3.1 Low-Speed Clock                                                           |      |

| 6.3.1.1 Low-Speed Clock Generation Circuit (32.768 crystal oscillation circuit) |      |

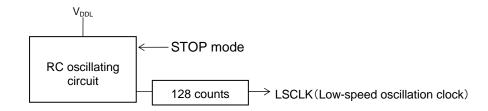

| 6.3.1.2 Low-speed clock generation circuit (built-in RC oscillating circuit)    |      |

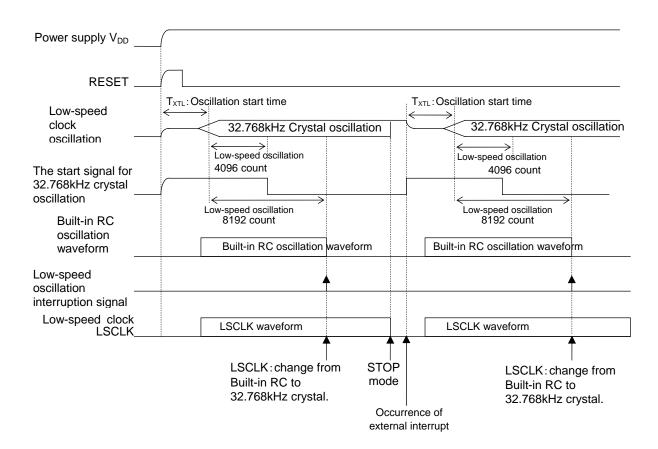

| 6.3.1.3 Operation of the Low-Speed Clock Generation Circuit                     |      |

| 6.3.2 High-Speed Clock                                                          |      |

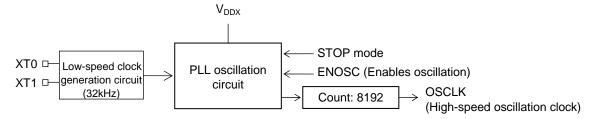

| 6.3.2.1 Built-in PLL Oscillation Mode                                           |      |

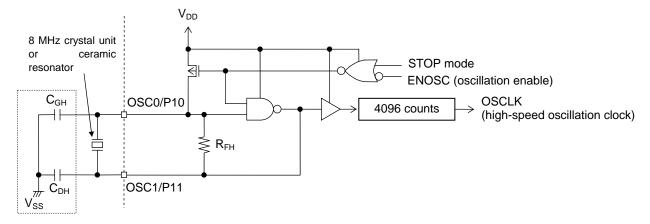

| 6.3.2.2 Crystal/Ceramic Oscillation Mode                                        |      |

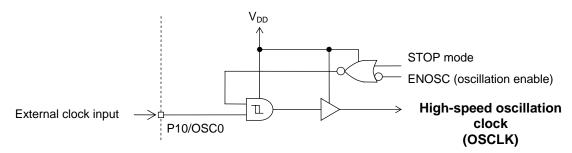

| 6.3.2.3 High-Speed External Clock Input Mode                                    |      |

| 6.3.2.4 Operation of High-Speed Clock Generation Circuit                        | 6-12 |

| 6.3.3     | Switching of System Clock                                                         | 6-14 |

|-----------|-----------------------------------------------------------------------------------|------|

|           | gister setup of the port                                                          |      |

| 6.4.1     | When the P21 pin (OUTCLK:output) operates as the high-speed clock output function |      |

| 6.4.2     | When the P20 pin (LSCLK:output) operates as the low-speed clock output function   |      |

| 6.4.3     | When the P36 pin (LSCLK:output) operates as the low-speed clock output function   |      |

| 0.1.5     | Then the 130 pm (25022100 diput) operates as the 10% speed clock output ranction  | 0 17 |

|           |                                                                                   |      |

| Chapter 7 |                                                                                   |      |

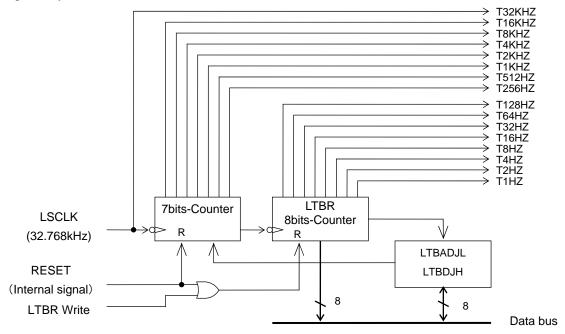

| 7. Time   | Base Counter                                                                      | 7-1  |

|           | verview                                                                           |      |

| 7.1.1     | Features                                                                          | 7-1  |

| 7.1.2     | Configuration                                                                     |      |

| 7.2 De    | escription of Registers                                                           |      |

| 7.2.1     | List of Registers                                                                 |      |

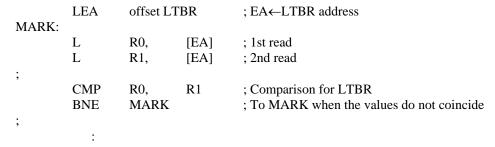

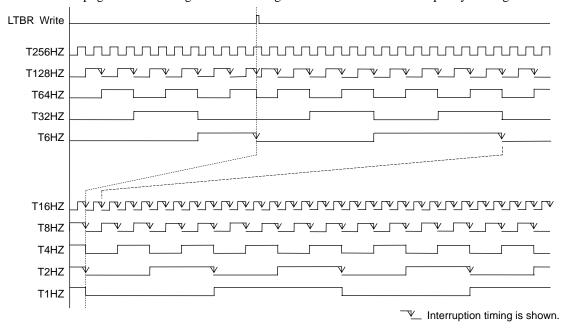

| 7.2.2     | Low-Speed Time Base Counter (LTBR)                                                |      |

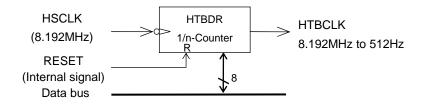

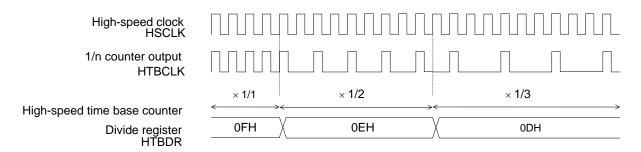

| 7.2.3     | High-Speed Time Base Counter Divide Register (HTBDR)                              |      |

| 7.2.4     | Low-Speed Time Base Counter Frequency Adjustment Registers L and H                |      |

|           | (LTBADJL, LTBADJH)                                                                | 7-6  |

| 7.3 De    | escription of Operation                                                           |      |

| 7.3.1     | Low-Speed Time Base Counter                                                       |      |

| 7.3.2     | High-Speed Time Base Counter                                                      |      |

| 7.3.3     | Low-Speed Time Base Counter Frequency Adjustment Function                         |      |

|           |                                                                                   |      |

| Chapter 8 |                                                                                   |      |

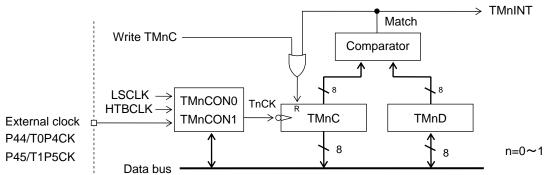

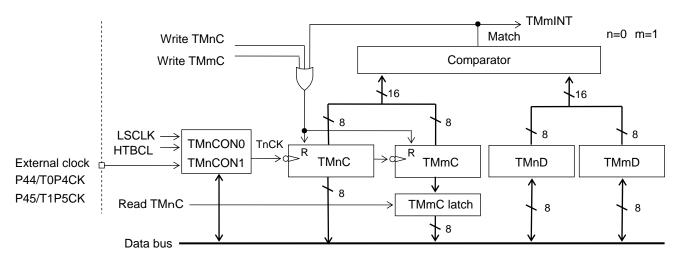

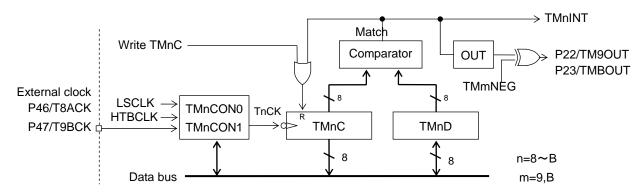

| 8. Time   | rs                                                                                | 8-1  |

| 8.1 Ov    | rerview                                                                           | 8-1  |

| 8.1.1     | Features                                                                          | 8-1  |

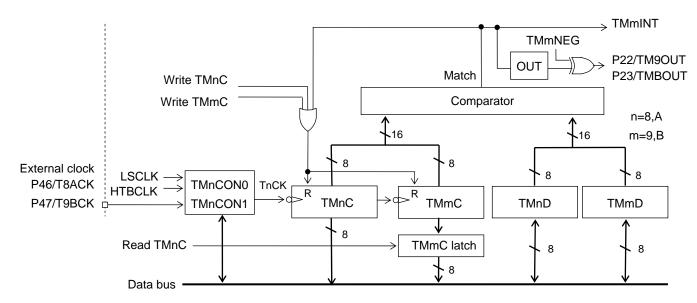

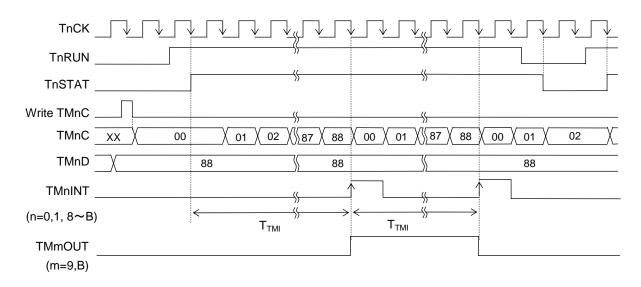

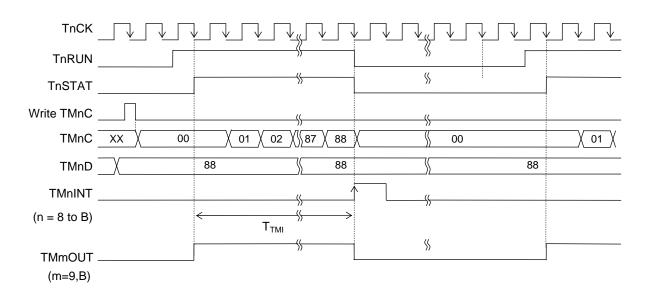

| 8.1.2     | Configuration                                                                     | 8-1  |

| 8.2 De    | escription of Registers                                                           | 8-3  |

| 8.2.1     | List of Registers                                                                 | 8-3  |

| 8.2.2     | Timer 0 Data Register (TM0D)                                                      | 8-4  |

| 8.2.3     | Timer 1 Data Register (TM1D)                                                      | 8-5  |

| 8.2.4     | Timer 8 Data Register (TM8D)                                                      | 8-6  |

| 8.2.5     | Timer 9 Data Register (TM9D)                                                      | 8-7  |

| 8.2.6     | Timer A Data Register (TMAD)                                                      | 8-8  |

| 8.2.7     | Timer B Data Register (TMBD)                                                      | 8-9  |

| 8.2.8     | Timer 0 Counter Register (TM0C)                                                   | 8-10 |

| 8.2.9     | Timer 1 Counter Register (TM1C)                                                   | 8-11 |

| 8.2.10    | Timer 8 Counter Register (TM8C)                                                   | 8-12 |

| 8.2.11    | Timer 9 Counter Register (TM9C)                                                   | 8-13 |

| 8.2.12    | Timer A Counter Register (TMAC)                                                   | 8-14 |

| 8.2.13    | Timer B Counter Register (TMBC)                                                   | 8-15 |

| 8.2.14    | Timer 0 Control Register 0 (TM0CON0)                                              |      |

| 8.2.15    | Timer 1 Control Register 0 (TM1CON0)                                              |      |

| 8.2.16    | Timer 8 Control Register 0 (TM8CON0)                                              |      |

| 8.2.17    | Timer 9 Control Register 0 (TM9CON0)                                              |      |

| 8.2.18    | Timer A Control Register 0 (TMACON0)                                              |      |

| 8.2.19    | Timer B Control Register 0 (TMBCON0)                                              |      |

| 8.2.20    | Timer 0 Control Register 1 (TM0CON1)                                              |      |

| 8.2.21    | Timer 1 Control Register 1 (TM1CON1)                                              |      |

| 8.2.22    | Timer 8 Control Register 1 (TM8CON1)                                              |      |

| 8.2.23    | Timer 9 Control Register 1 (TM9CON1)                                              |      |

|           | Timer A Control Register 1 (TMACON1)                                              |      |

|           | Timer B Control Register 1 (TMBCON1)                                              |      |

|           | escription of Operation                                                           |      |

# Chapter 9

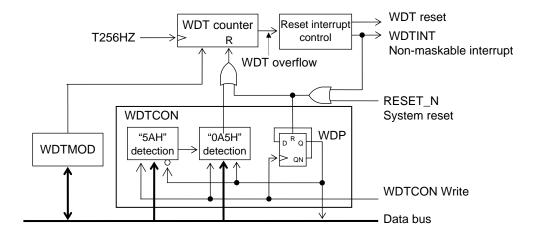

|           | hdog Timer                                                                                                        |       |

|-----------|-------------------------------------------------------------------------------------------------------------------|-------|

| 9.1 Ov    | verview                                                                                                           |       |

| 9.1.1     | Features                                                                                                          |       |

| 9.1.2     | Configuration                                                                                                     | 9-1   |

| 9.2 De    | escription of Registers                                                                                           | 9-2   |

| 9.2.1     | List of Registers                                                                                                 |       |

| 9.2.2     | Watchdog Timer Control Register (WDTCON)                                                                          | 9-3   |

| 9.2.3     | Watchdog Timer Mode Register (WDTMOD)                                                                             | 9-4   |

| 9.3 De    | escription of Operation                                                                                           |       |

| 9.3.1     | Handling example when you do not want to use the watch dog timer                                                  | 9-7   |

| Chapter 1 | 0                                                                                                                 |       |

| 10. PWN   | 1                                                                                                                 | 10-1  |

| 10.1 Ov   | rerview                                                                                                           | 10-1  |

| 10.1.1    | Features                                                                                                          | 10-1  |

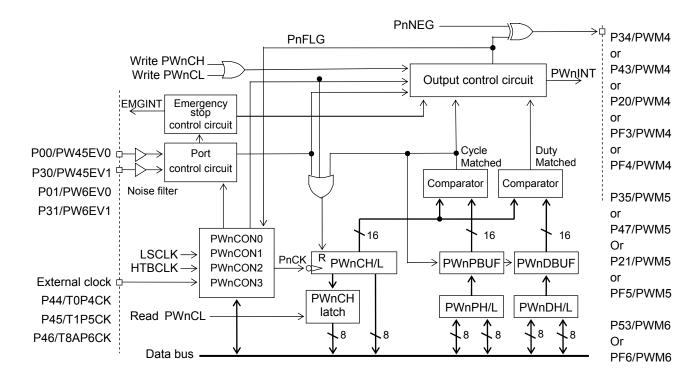

| 10.1.2    | Configuration                                                                                                     | 10-2  |

| 10.1.3    | List of Pins                                                                                                      | 10-4  |

| 10.2 De   | escription of Registers                                                                                           | 10-4  |

| 10.2.1    | List of Registers                                                                                                 | 10-4  |

| 10.2.2    | PWM4 Period Registers (PW4PL, PW4PH)                                                                              | 10-5  |

| 10.2.3    | PWM4 Duty Registers (PW4DL, PW4DH)                                                                                | 10-6  |

| 10.2.4    | PWM4 Counter Registers (PW4CH, PW4CL)                                                                             | 10-7  |

| 10.2.5    | PWM4 Control Register 0 (PW4CON0)                                                                                 | 10-8  |

| 10.2.6    | PWM4 Control Register 1 (PW4CON1)                                                                                 | 10-10 |

| 10.2.7    | PWM4 Control Register 2 (PW4CON2)                                                                                 | 10-11 |

| 10.2.8    | PWM4 Control Register 3 (PW4CON3)                                                                                 | 10-13 |

|           | PWM5 Period Registers (PW5PL, PW5PH)                                                                              |       |

| 10.2.10   | PWM5 Duty Registers (PW5DL, PW5DH)                                                                                | 10-15 |

| 10.2.11   | PWM5 Counter Registers (PW5CH, PW5CL)                                                                             | 10-16 |

| 10.2.12   | PWM5 Control Register 0 (PW5CON0)                                                                                 | 10-17 |

| 10.2.13   | PWM5 Control Register 1 (PW5CON1)                                                                                 | 10-19 |

| 10.2.14   | - PWM5 Control Register 2 (PW5CON2)                                                                               | 10-20 |

| 10.2.15   | PWM6 Period Registers (PW6PL, PW6PH)                                                                              | 10-22 |

| 10.2.16   | PWM6 Duty Registers (PW6DL, PW6DH)                                                                                | 10-23 |

| 10.2.17   | PWM6 Counter Registers (PW6CH, PW6CL)                                                                             | 10-24 |

| 10.2.18   | PWM6 Control Register 0 (PW6CON0)                                                                                 | 10-25 |

| 10.2.19   | PWM6 Control Register 1 (PW6CON1)                                                                                 | 10-27 |

| 10.2.19   | PWM6 Control Register 2 (PW6CON2)                                                                                 | 10-28 |

|           | escription of Operation                                                                                           |       |

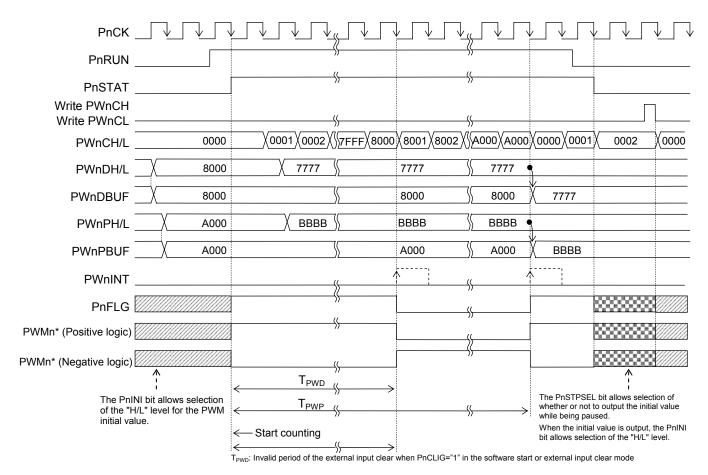

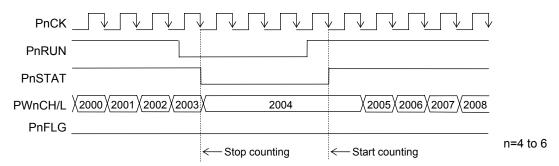

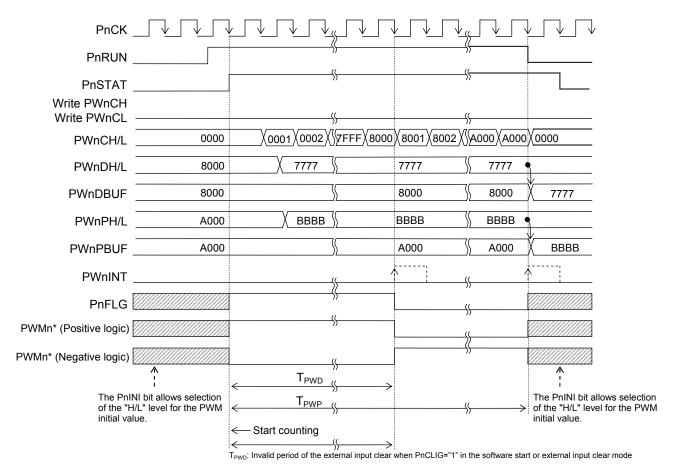

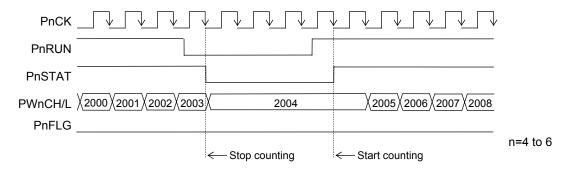

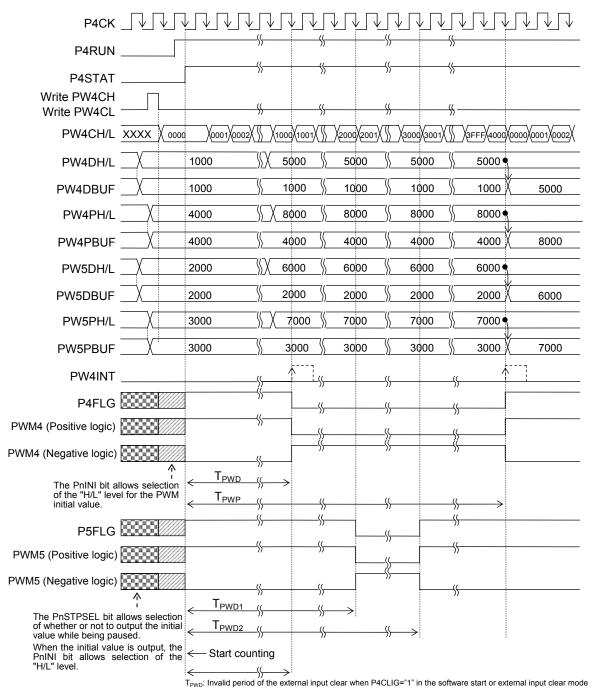

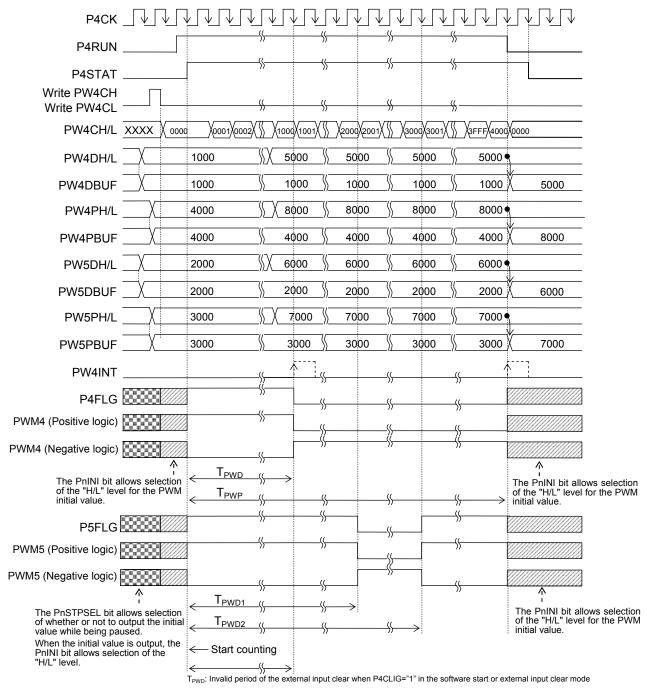

| 10.3.1    | Repeat Mode with PWM4 and PWM5 Standalone Mode (P45MD="0", PnMD="0")                                              | 10-32 |

| 10.3.2    | One-shot Mode with PWM4 and PWM5 Standalone Mode (P45MD="0", PnMD="1")                                            | 10-34 |

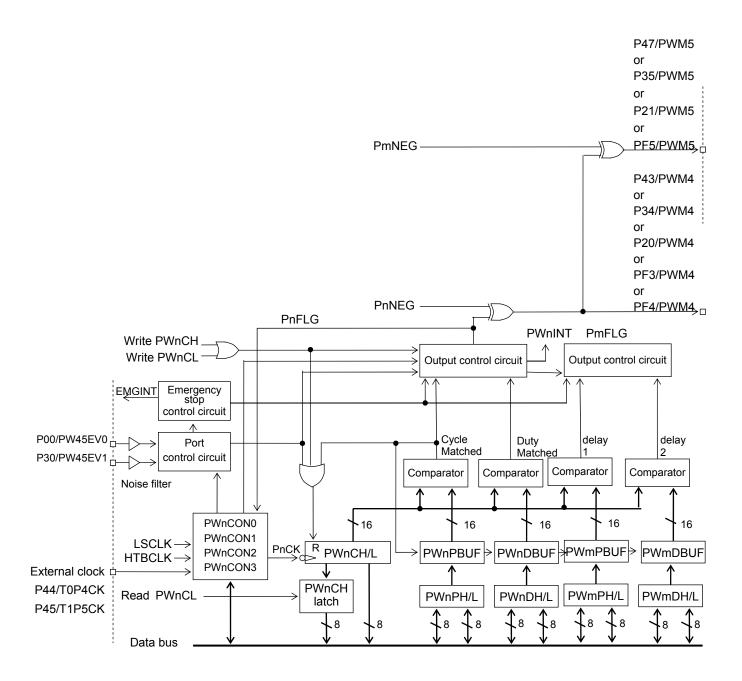

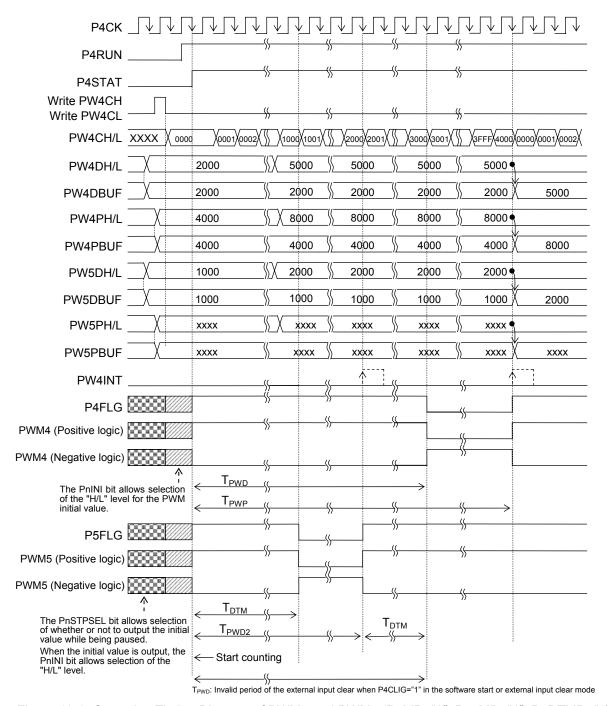

| 10.3.3    | Repeat Mode with PWM4 and PWM5 Cooperation Mode (Dead Time Setting Is Not Used) (P45MD="1", P4DTMD="0", P4MD="0") | 10.26 |

| 10.3.4    | One-shot Mode with PWM4 and PWM5 Cooperation Mode (Dead Time Setting Is Not Used)                                 | 10-30 |

|           | (P45MD="1", P4DTMD="0", P4MD="1")                                                                                 | 10-39 |

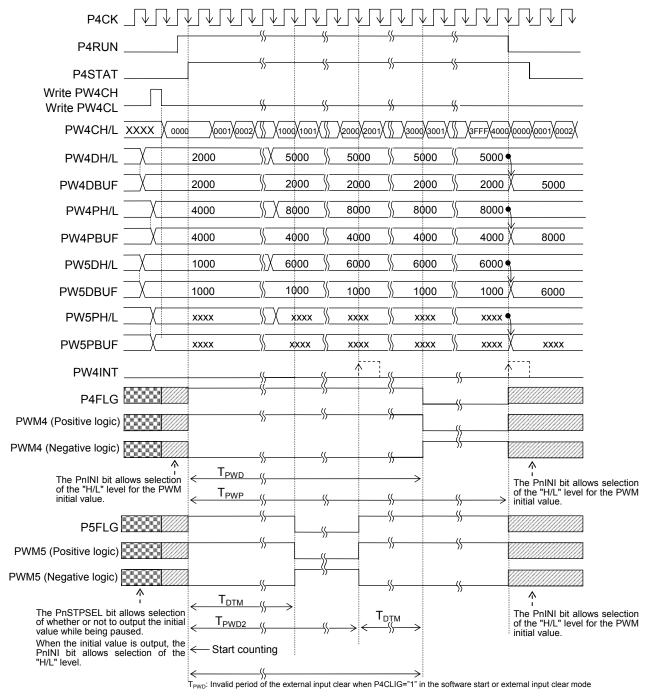

| 10.3.5    | Repeat Mode with PWM4 and PWM5 Cooperation Mode (Dead Time Setting Is Used)                                       | 10.42 |

| 100       | (P45MD="1", P4DTMD="1", P4MD="0")                                                                                 | 10-42 |

| 10.3.6    | One-shot Mode with PWM4 and PWM5 Cooperation Mode (Dead Time Setting Is Used)                                     |       |

| 40.5 =    | (P45MD="1", P4DTMD="1", P4MD="1")                                                                                 |       |

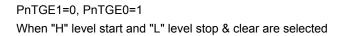

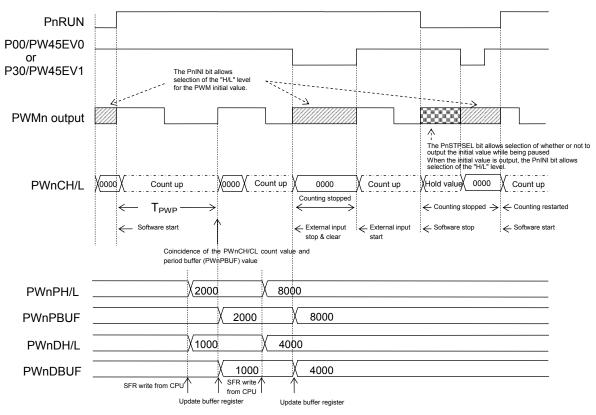

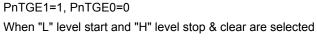

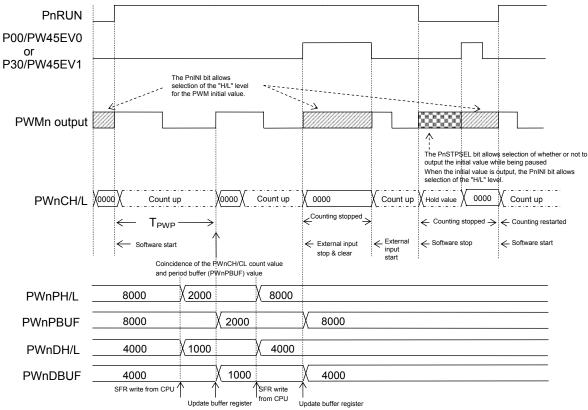

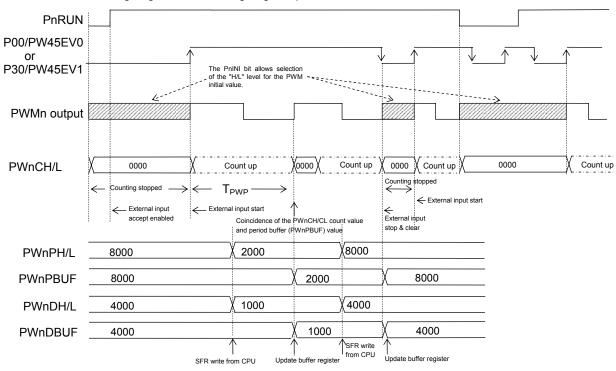

|           | Start, Stop, and Clear Operations of PWM4 and PWM5 by External Input Control                                      |       |

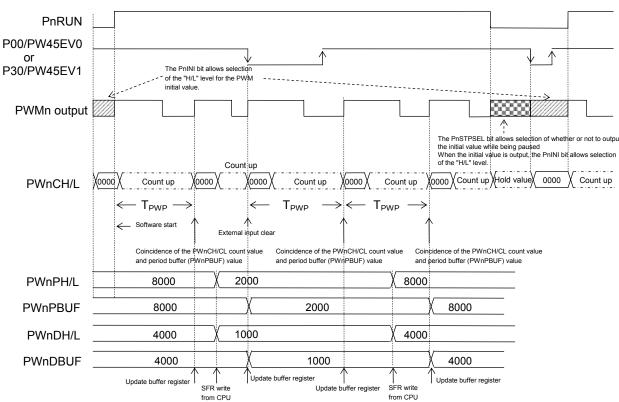

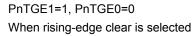

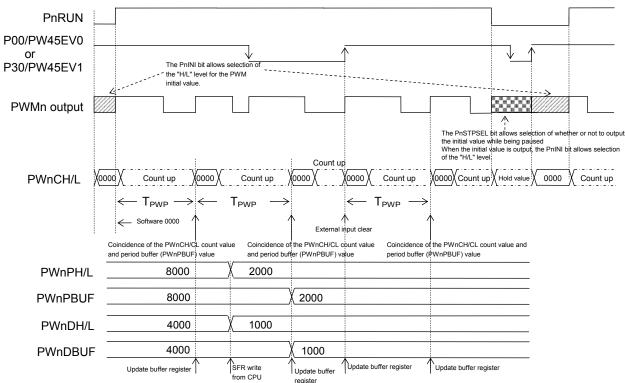

|           | 7.1 Software Start Mode                                                                                           |       |

|           | 7.2 Software Start or External Input Start Mode                                                                   |       |

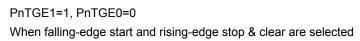

| 10.3.     | 7.3 External Input Start Mode                                                                                     | 10-53 |

| 10.3.     | 7.4 Software Start or External Input Clear Mode                                                                   | 10-55 |

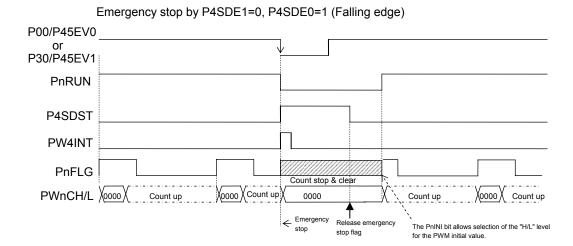

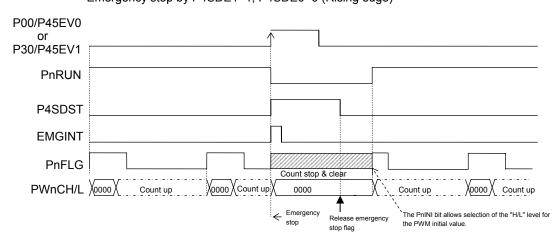

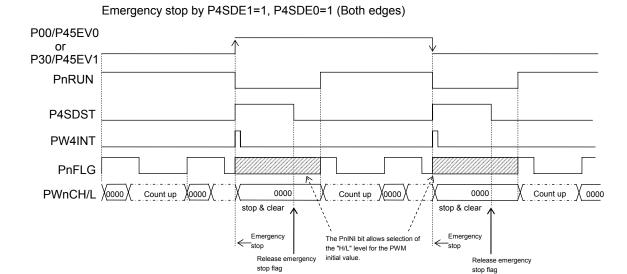

| 10.3.8    | Emergency Stop Operation                                                              | 10-58 |

|-----------|---------------------------------------------------------------------------------------|-------|

| 10.4 Sp   | ecifying Port Registers                                                               | 10-60 |

| 10.4.1    | Functioning P34 Pin (PWM4) as PWM Output                                              | 10-60 |

| 10.4.2    | Functioning P43 Pin (PWM4) as PWM Output                                              | 10-61 |

|           | Functioning P35 Pin (PWM5) as PWM Output                                              |       |

|           | Functioning P47 Pin (PWM5) as PWM Output                                              |       |

|           | Functioning P53 Pin (PWM6) as PWM Output                                              |       |

|           |                                                                                       |       |

|           |                                                                                       |       |

| Chapter 1 | 1                                                                                     |       |

| •         |                                                                                       |       |

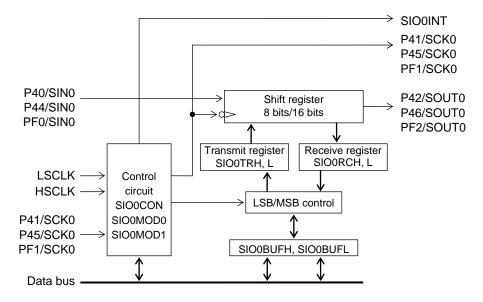

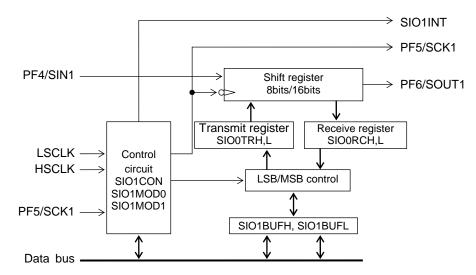

|           | hronous Serial Port                                                                   |       |

|           | verview                                                                               |       |

|           | Features                                                                              |       |

|           | Configuration                                                                         |       |

|           | List of Pins                                                                          |       |

|           | escription of Registers                                                               |       |

|           | List of Registers                                                                     |       |

|           | Serial Port Transmit/Receive Buffers (SIO0BUFL, SIO0BUFH)                             |       |

|           | Serial Port Transmit/Receive Buffers (SIO1BUFL, SIO1BUFH)                             |       |

| 11.2.4    | Serial Port Control Register (SIO0CON)                                                | 11-7  |

| 11.2.5    | Serial Port Control Register (SIO1CON)                                                | 11-8  |

| 11.2.6    | Serial Port Mode Register 0 (SIO0MOD0)                                                | 11-9  |

| 11.2.7    | Serial Port Mode Register 0 (SIO1MOD0)                                                | 11-10 |

| 11.2.8    | Serial Port Mode Register 1 (SIO0MOD1)                                                | 11-11 |

|           | Serial Port Mode Register 1 (SIO1MOD1)                                                |       |

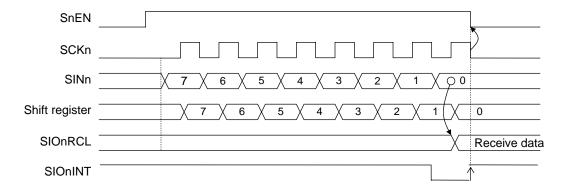

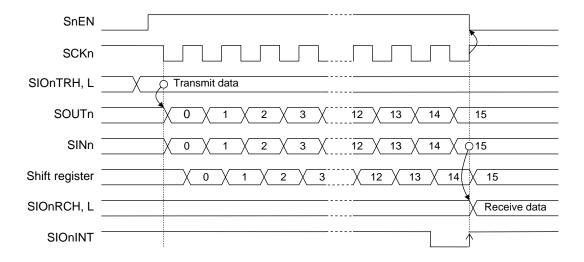

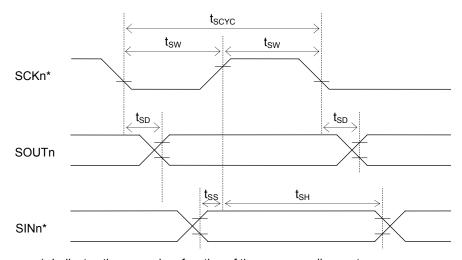

|           | escription of Operation                                                               |       |

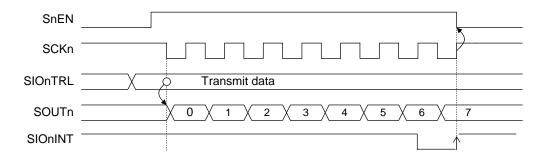

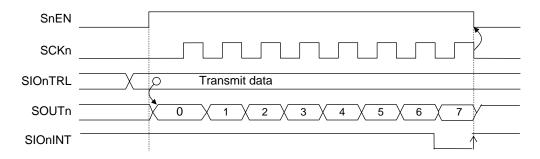

|           | Transmit Operation                                                                    |       |

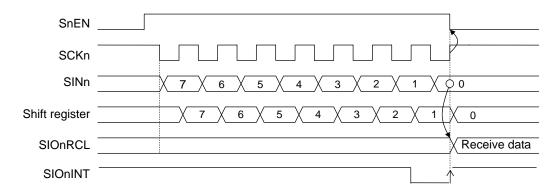

|           | Receive Operation.                                                                    |       |

|           | Transmit/Receive Operation                                                            |       |

|           | gister setup of the port                                                              |       |

|           | When operating the SSIO function in master mode using P42 pin (SOUT0:output), P41 pin | 11 10 |

| 11.4.1    | (SCK0:input/output), and P40 pin (SIN0:input)                                         | 11 16 |

| 11 4 2    | When operating the SSIO function in slave mode using P42 pin (SOUT0:output), P41 pin  | 11-10 |

| 11.4.2    | (SCK0:input/output), and P40 pin (SIN0:input)                                         | 11 17 |

| 11 4 2    |                                                                                       | 11-1/ |

| 11.4.3    | When operating the SSIO function in master mode using P52 pin (SOUT1:output), P51 pin | 11 10 |

| 11 4 4    | (SCK1:input/output), and P50 pin (SIN1:input)                                         | 11-18 |

| 11.4.4    | When operating the SSIO1 function in slave mode using P52 pin (SOUT1:output), P51 pin | 11 10 |

|           | (SCK1:input/output), and P50 pin (SIN1:input).                                        | 11-19 |

| Chaptan 1 | 3                                                                                     |       |

| Chapter 1 | <u>Z</u>                                                                              |       |

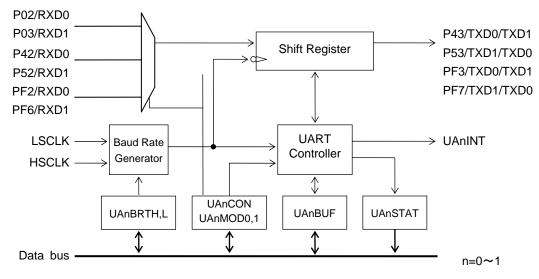

| 12. UAR   | Т                                                                                     | 12-1  |

| 12.1 Ov   | erview                                                                                | 12-1  |

| 12.1.1    | Features                                                                              | 12-1  |

| 12.1.2    | Configuration                                                                         | 12-1  |

| 12.1.3    | List of Pins                                                                          | 12-2  |

|           | escription of Registers                                                               |       |

|           | List of Registers                                                                     |       |

|           | UARTO Transmit/Receive Buffer (UA0BUF)                                                |       |

|           | UART1 Transmit/Receive Buffer (UA1BUF)                                                |       |

|           | UART0 Control Register (UA0CON)                                                       |       |

|           | UART1 Control Register (UA1CON)                                                       |       |

|           | UARTO Mode Register (UAOMODO)                                                         |       |

|           | UART1 Mode Register 0 (UA1MOD0)                                                       |       |

|           | UART1 Mode Register ( (UA1MOD0)                                                       |       |

|           | UART1 Mode Register 1 (UA1MOD1)                                                       |       |

|           |                                                                                       |       |

| 12.2.10   | UARTO Baud Rate Registers L, H (UAOBRTL, UAOBRTH)                                     | 12-11 |

| 12.2.11 UART1 Baud Rate Registers L, H (UA1BRTL, UA1BRTH)                                    | 12-12 |

|----------------------------------------------------------------------------------------------|-------|

| 12.2.12 UARTO Status Register (UAOSTAT)                                                      |       |

| 12.2.13 UART1 Status Register (UA1STAT)                                                      | 12-15 |

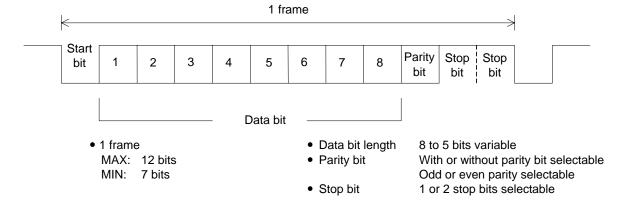

| 12.3 Description of Operation                                                                | 12-17 |

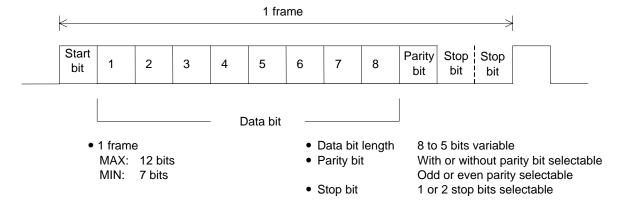

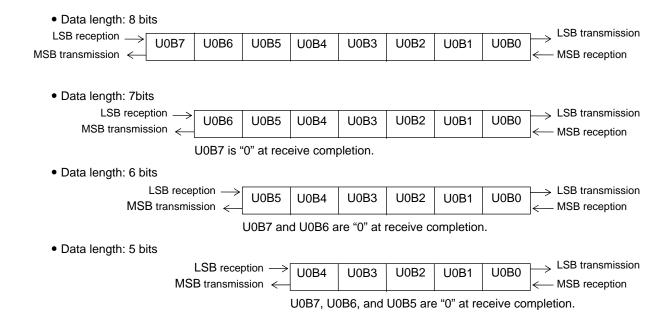

| 12.3.1 Transfer Data Format                                                                  |       |

| 12.3.2 Baud Rate                                                                             |       |

| 12.3.3 Transmit Data Direction                                                               |       |

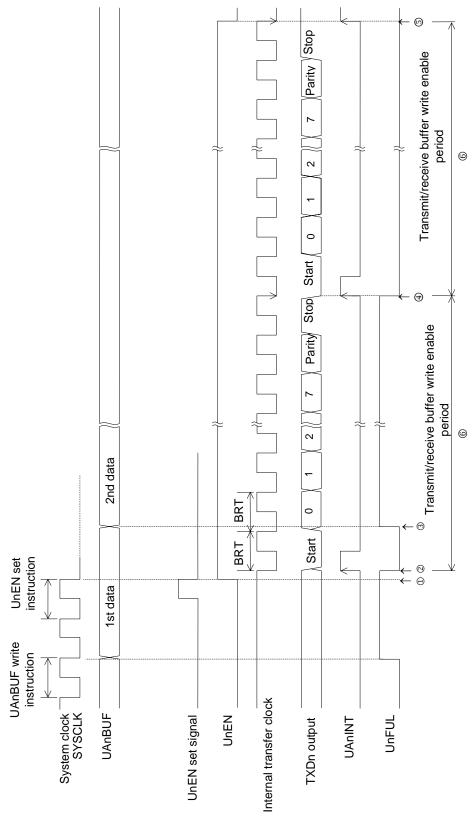

| 12.3.4 Transmit Operation                                                                    |       |

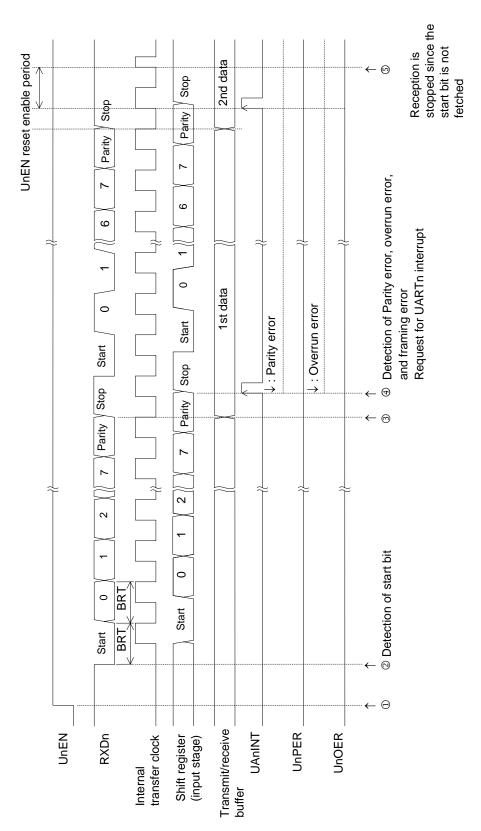

| 12.3.5 Receive Operation                                                                     |       |

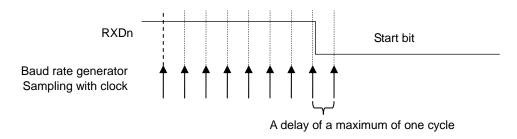

| 12.3.5.1 Detection of Start bit                                                              |       |

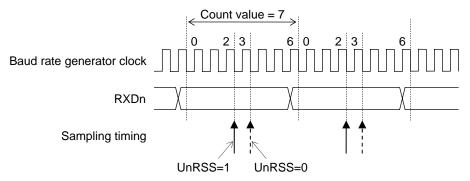

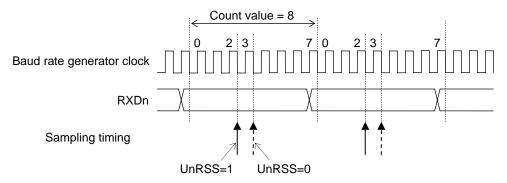

| 12.3.5.2 Sampling Timing                                                                     |       |

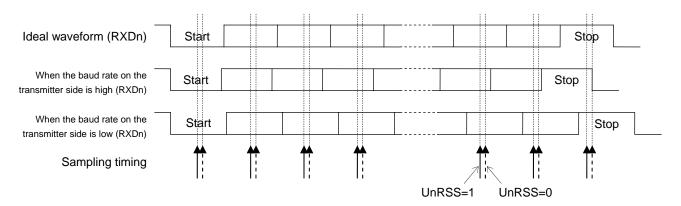

| 12.3.5.3 Reception Margin                                                                    |       |

| 12.4 Register setup of the port                                                              |       |

| 12.4.1 When operating the UART function using P43 pin (TXD0:output) and P42 pin (RDX0:input) |       |

| 12.4.2 When operating the UART function using P43 pin (TXD0:output) and P02 pin (RDX0:input) |       |

| 12.4.3 When operating the UART function using P53 pin (TXD1:output) and P52 pin (RDX1:input) |       |

| 12.4.4 When operating the UART function using P53 pin (TXD1:output) and P03 pin (RDX1:input) |       |

| 12.4.5 When operating the UART function using P53 pin (TXD0:output) and P42 pin (RDX0:input) |       |

| 12.4.6 When operating the UART function using P43 pin (TXD1:output) and P52 pin (RDX2:input) |       |

| 12.4.7 When operating the UART function using PF3 pin (TXD0:output) and PF2 pin (RXD0:input) |       |

| 12.4.7 When operating the UART function using PF7 pin (TXD1:output) and PF6 pin (RXD1:input) | 12-37 |

|                                                                                              |       |

| Chapter 13                                                                                   |       |

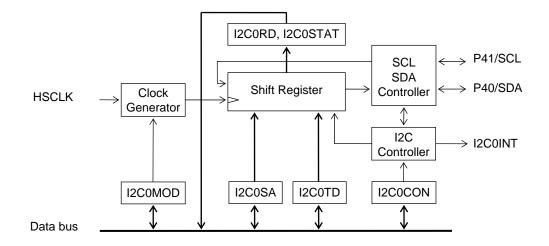

| 13. I <sup>2</sup> C Bus Interface                                                           | 12 1  |

| 13.1 Overview                                                                                |       |

| 13.1.1 Features                                                                              |       |

| 13.1.2 Configuration                                                                         |       |

| 13.1.3 List of Pins                                                                          |       |

| 13.2 Description of Registers                                                                |       |

| 13.2.1 List of Registers                                                                     |       |

| 13.2.2 I <sup>2</sup> C Bus 0 Receive Register (I2C0RD)                                      |       |

| 13.2.3 I <sup>2</sup> C Bus 0 Slave Address Register (I2C0SA)                                |       |

| 13.2.4 I <sup>2</sup> C Bus 0 Transmit Data Register (I2C0TD)                                |       |

| 13.2.5 I <sup>2</sup> C Bus 0 Control Register (I2C0CON)                                     |       |

| 13.2.6 I <sup>2</sup> C Bus 0 Mode Register (I2C0MOD)                                        |       |

| 13.2.7 I <sup>2</sup> C Bus 0 Status Register (I2C0STAT)                                     |       |

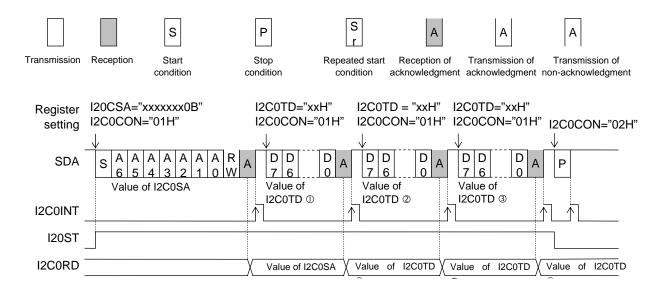

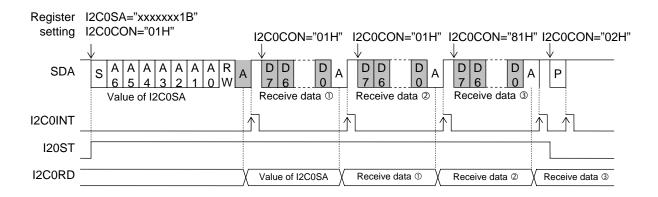

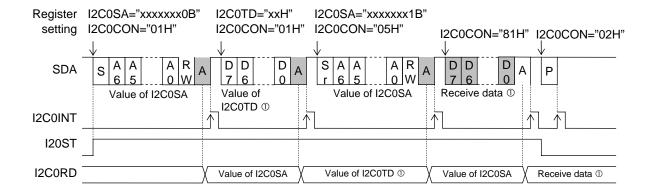

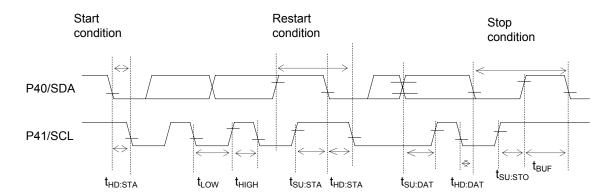

| 13.3 Description of Operation                                                                |       |

| 13.3.1 Communication Operating Mode                                                          |       |

| 13.3.1.1 Start Condition                                                                     |       |

| 13.3.1.2 Restart Condition                                                                   |       |

| 13.3.1.3 Slave Address Transmit Mode                                                         |       |

| 13.3.1.4 Data Transmit Mode                                                                  |       |

| 13.3.1.5 Data Receive Mode                                                                   |       |

| 13.3.1.6 Control Register Setting Wait State                                                 |       |

| 13.3.1.7 Stop Condition                                                                      |       |

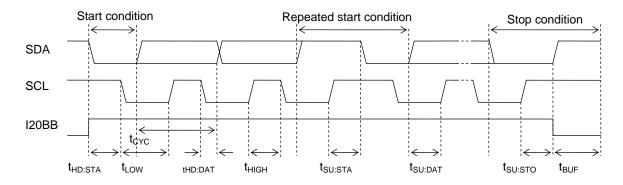

| 13.3.2 Communication Operation Timing                                                        |       |

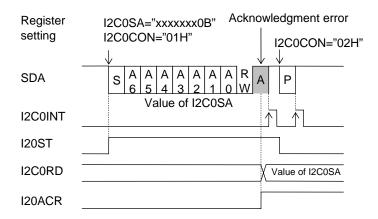

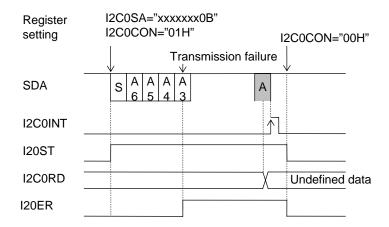

| 13.3.3 Operation Waveforms                                                                   | 13-12 |

| 13.4 Description of Operation                                                                |       |

| 13.4.1 Functioning P41(SCL) and P40(SDA) as the I2C                                          |       |

|                                                                                              |       |

| Chapter 14                                                                                   |       |

| 1                                                                                            |       |

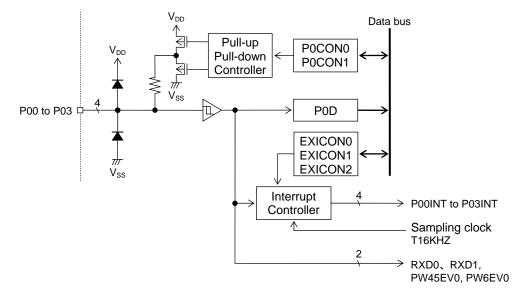

| 14. Port 0                                                                                   |       |

| 14.1 Overview                                                                                |       |

| 14.1.1 Features                                                                              |       |

| 14.1.2 Configuration                                                                         |       |

| 14.1.3 List of Pins                                                                          | 14-2  |

|                                                                                              |       |

| 14.2 Description of Registers                                       | 14-3 |

|---------------------------------------------------------------------|------|

| 14.2.1 List of Registers                                            |      |

| 14.2.2 Port 0 Data Register (P0D)                                   |      |

| 14.2.3 Port 0 Control Registers 0, 1 (P0CON0, P0CON1)               |      |

| 14.2.4 External Interrupt Control Registers 0, 1 (EXICON0, EXICON1) |      |

| 14.2.5 External Interrupt Control Register 2 (EXICON2)              |      |

| 14.3 Description of Operation                                       |      |

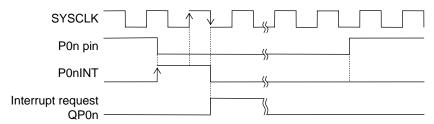

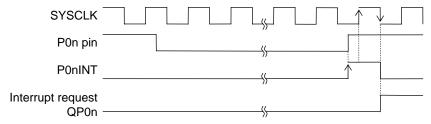

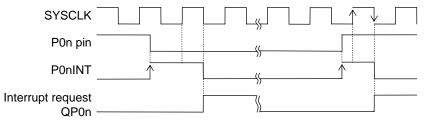

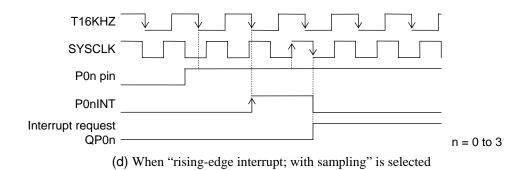

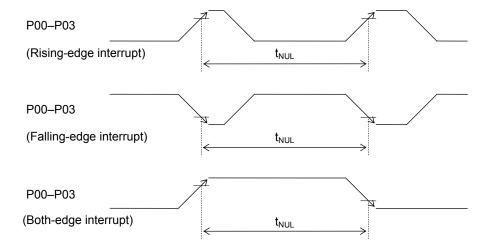

| 14.3.1 External Interrupt                                           |      |

| 14.3.2 Interrupt Request                                            |      |

| Chapter 15                                                          |      |

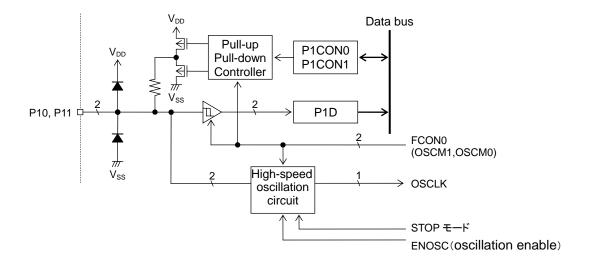

| 15. Port 1                                                          | 15-1 |

| 15.1 Overview                                                       |      |

| 15.1.1 Features                                                     |      |

| 15.1.2 Configuration                                                |      |

| 15.1.3 List of Pins                                                 |      |

| 15.2 Description of Registers                                       |      |

| 15.2.1 List of Registers                                            |      |

| 15.2.2 Port 1 Data Register (P1D)                                   |      |

| 15.2.3 Port 1 Control Registers 0,1 (P1CON0, P1CON1)                |      |

| 15.3 Description of Operation                                       |      |

| 15.3.1 Input Port Function                                          |      |

| Chapter 16                                                          |      |

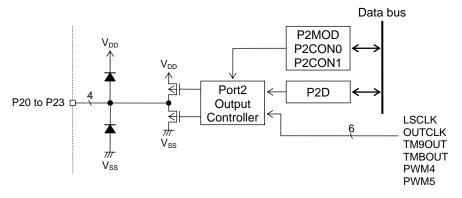

| 16. Port 2                                                          |      |

| 16.1 Overview                                                       |      |

| 16.1.1 Features                                                     |      |

| 16.1.2 Configuration                                                |      |

| 16.1.3 List of Pins                                                 |      |

| 16.2 Description of Registers                                       |      |

| 16.2.1 List of Registers                                            |      |

| 16.2.2 Port 2 Data Register (P2D)                                   |      |

| 16.2.3 Port 2 control registers 0, 1 (P2CON0, P2CON1)               |      |

| 16.2.4 Port 2 Mode Register (P2MOD)                                 |      |

| 16.3 Description of Operation                                       |      |

| 16.3.1 Output Port Function                                         |      |

| 16.3.2 Secondary Function                                           |      |

| Chapter 17                                                          |      |

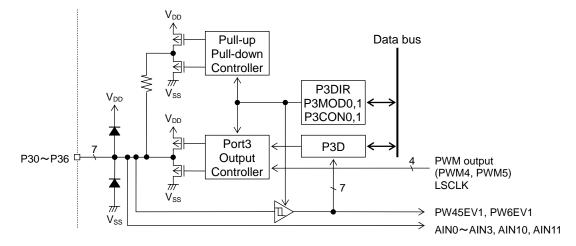

| 17. Port 3                                                          | 17-1 |

| 17.1 Overview                                                       |      |

| 17.1.1 Features                                                     |      |

| 17.1.2 Configuration                                                |      |

| 17.1.3 List of Pins                                                 |      |

| 17.2 Description of Registers                                       |      |

| 17.2.1 List of Registers                                            |      |

| 17.2.2 Port 3 Data Register (P3D)                                   |      |

| 17.2.3 Port 3 Direction Register (P3DIR)                            |      |

| 17.2.4 Port 3 control registers 0, 1 (P3CON0, P3CON1)               |      |

| 17.2.5 Port 3 Mode Registers 0, 1 (P3MOD0, P3MOD1)                  |      |

| 17.3 Description of Operation                                       |      |

| 17.3.1 Input/Output Port Functions                                  |      |

| 17.3.2 Secondary Function                                           |      |

| •                                                                   |      |

# Chapter 18

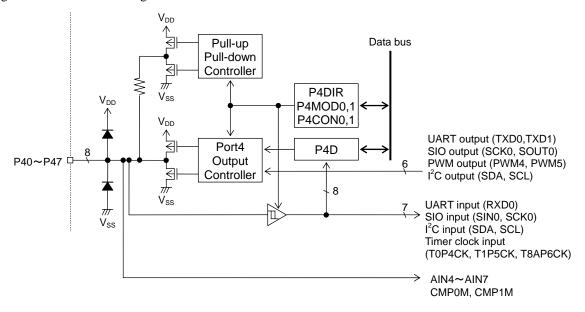

|           | 4                                                                  |       |

|-----------|--------------------------------------------------------------------|-------|

|           | verview                                                            |       |

|           | Features                                                           |       |

|           | Configuration                                                      |       |

|           | List of Pins                                                       |       |

|           | escription of Registers                                            |       |

|           | List of Registers                                                  |       |

|           | Port 4 Data Register (P4D)                                         |       |

|           | Port 4 Direction Register (P4DIR)                                  |       |

|           | Port 4 Control Registers 0, 1 (P4CON0, P4CON1)                     |       |

|           | Port 4 Mode Registers 0, 1 (P4MOD0, P4MOD1)                        |       |

|           | escription of Operation                                            |       |

|           | Input/Output Port Functions                                        |       |

| 16.5.2    | Secondary and Ternary Functions                                    | 10-11 |

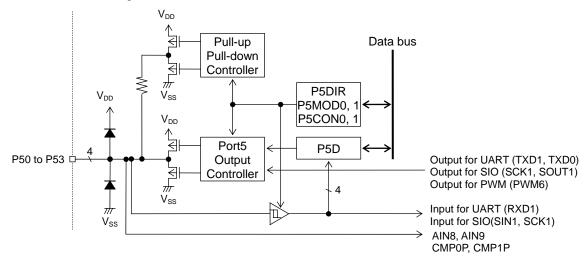

| Chapter   | 19                                                                 |       |

|           | 5                                                                  |       |

|           | verview                                                            |       |

|           | Features                                                           |       |

|           | Configuration                                                      |       |

|           | List of Pins                                                       |       |

|           | escription of Registers                                            |       |

|           | List of Registers                                                  |       |

|           | Port 5 Data Register (P5D)                                         |       |

|           | Port 5 Direction Register (P5DIR)                                  |       |

|           | Port 5 Control Registers 0, 1 (P5CON0, P5CON1)                     |       |

|           | Port 5 Mode Registers 0, 1 (P5MOD0, P5MOD1)escription of Operation |       |

|           | Input/Output Port Functions                                        |       |

| 17.3.1    | input Output Fort Functions                                        |       |

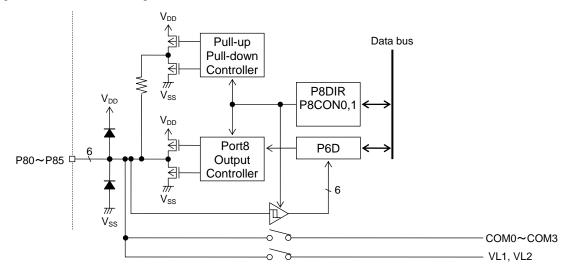

| Chapter 2 | 20                                                                 |       |

| 20. Port  | 8                                                                  | 20-1  |

| 20.1 O    | verview                                                            | 20-1  |

| 20.1.1    | Features                                                           | 20-1  |

| 20.1.2    | Configuration                                                      | 20-1  |

|           | List of Pins                                                       |       |

|           | escription of Registers                                            |       |

|           | List of Registers                                                  |       |

|           | Port 5 Data Register (P8D)                                         |       |

|           | Port 5 Direction Register (P8DIR)                                  |       |

|           | Port 5 Control Registers 0, 1 (P8CON0, P8CON1)                     |       |

|           | escription of Operation                                            |       |

| 20.3.1    | Input/Output Port Functions                                        | 20-8  |

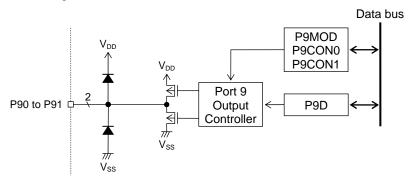

| Chapter 2 | 21                                                                 |       |

| 21. Port  | 9                                                                  | 21-1  |

| 21.1 O    | verview                                                            | 21-1  |

| 21.1.1    | Features                                                           | 21-1  |

| 21.1.2    | Configuration                                                      | 21-1  |

|           | List of Pins                                                       |       |

|           | escription of Registers                                            |       |

|           | List of Registers                                                  |       |

| 21.2.2    | Port 9 Data Register (P9D)                                         | 21-3  |

| 21.2.4    | Port 9 Control Registers 0, 1 (P9CON0, P9CON1)                     | 21-4  |

| 21.3 Description of Operation                                  | 21-5  |

|----------------------------------------------------------------|-------|

| 21.3.1 Output Port Functions                                   |       |

| •                                                              |       |

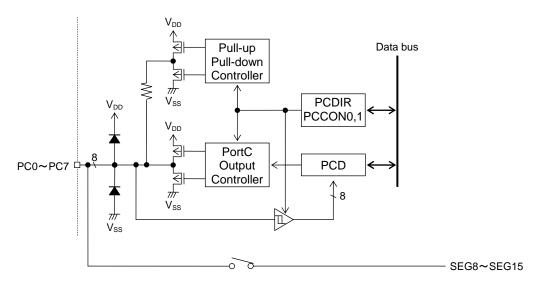

| Chapter 22                                                     |       |

| 22. Port C                                                     | 22-1  |

| 22.1 Overview                                                  |       |

| 22.1.1 Features                                                |       |

| 22.1.2 Configuration                                           |       |

| 22.1.2 Configuration                                           |       |

| 22.1.3 List of Phis                                            |       |

|                                                                |       |

| 22.2.1 List of Registers                                       |       |

| 22.2.2 Port C Data Register (PCD)                              |       |

| 22.2.3 Port C Direction Register (PCDIR)                       |       |

| 22.2.4 Port C control registers 0, 1 (PCCON0, PCCON1)          |       |

| 22.3 Description of Operation                                  |       |

| 22.3.1 Input/Output Port Functions                             |       |

| 22.3.2 Secondary Function                                      | 22-8  |

| Chapter 23                                                     |       |

| -                                                              |       |

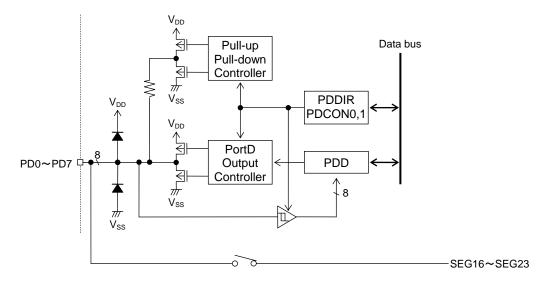

| 23. Port D                                                     | -     |

| 23.1 Overview                                                  |       |

| 23.1.1 Features                                                |       |

| 23.1.2 Configuration                                           |       |

| 23.1.3 List of Pins                                            |       |

| 23.2 Description of Registers                                  |       |

| 23.2.1 List of Registers                                       | 23-3  |

| 23.2.2 Port D Data Register (PDD)                              |       |

| 23.2.3 Port D Direction Register (PDDIR)                       | 23-5  |

| 23.2.4 Port D control registers 0, 1 (PDCON0, PDCON1)          |       |

| 23.3 Description of Operation                                  |       |

| 23.3.1 Input/Output Port Functions                             |       |

| 23.3.2 Secondary Function                                      |       |

| Chapter 24                                                     |       |

| -                                                              | 24.1  |

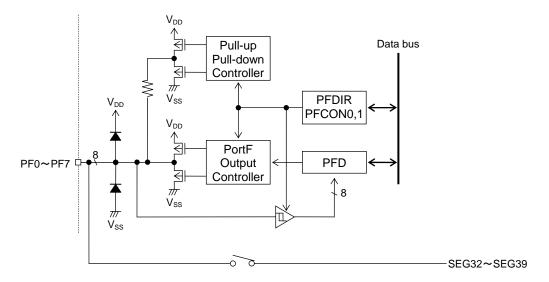

| 24. Port F                                                     |       |

| 24.1 Overview                                                  |       |

| 24.1.1 Features                                                |       |

| 24.1.2 Configuration                                           |       |

| 24.1.3 List of Pins                                            |       |

| 24.2 Description of Registers                                  |       |

| 24.2.1 List of Registers                                       |       |

| 24.2.2 Port D Data Register (PFD)                              |       |

| 24.2.3 Port D Direction Register (PFDIR)                       |       |

| 24.2.4 Port D control registers 0, 1 (PFCON0, PFCON1)          |       |

| 24.2.5 Port F Mode Registers 0, 1 (PFMOD0, PFMOD1)             |       |

| 24.3 Description of Operation                                  |       |

| 24.3.1 Input/Output Port Functions                             |       |

| 24.3.2 Secondary, tertiary and fourthly functions              | 24-10 |

| Chapter 25                                                     |       |

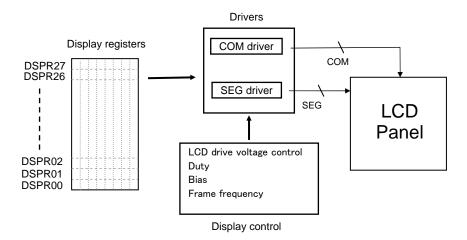

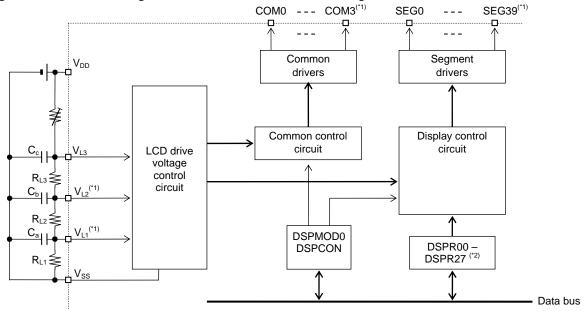

| 25. LCD Drivers                                                | 25_1  |

| 25.1 Overview                                                  |       |

| 25.1.1 Features                                                |       |

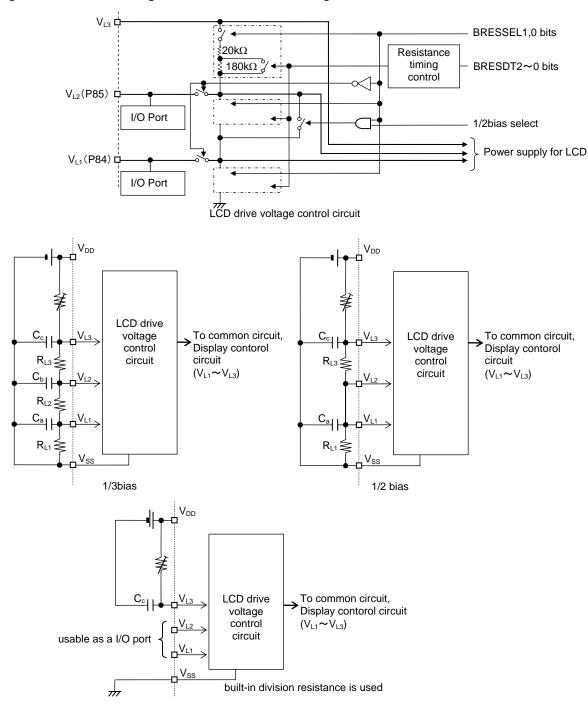

| 25.1.1 Features 25.1.2 Configuration of the LCD Drivers 25.1.2 |       |

| 25.1.2 Configuration of the LCD driver voltage control circui  |       |

| 23.1.3 Comiguration of the LCD three voltage collifor effcul   | t     |

| 25.1.4    | List of Pins                                                                                                                  | 25-4  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|-------|

| 25.2 De   | scription of Registers                                                                                                        | 25-5  |

| 25.2.1    | List of Registers                                                                                                             | 25-5  |

| 25.2.2    | Bias Circuit Control Register 0 (BIASCON)                                                                                     | 25-6  |

| 25.2.3    | Display Mode Register 0 (DSPMOD0)                                                                                             | 25-7  |

|           | Display Control Register (DSPCON)                                                                                             |       |

|           | Bias circuit Mode Register 0 (BIASMOD)                                                                                        |       |

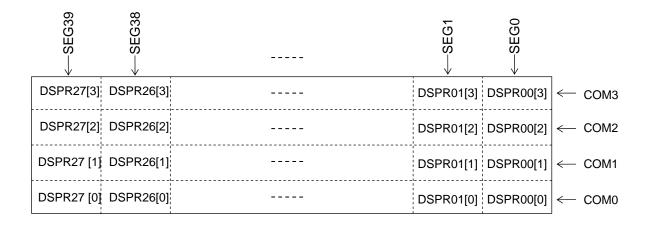

| 25.2.6    | Display Registers (DSPR00 to DSPR17, DSPR20 to DSPR27)                                                                        | 25-10 |

|           | LCD port segment selection register 1 (LSELS1)                                                                                |       |

|           | LCD port segment selection register 2 (LSELS2)                                                                                |       |

|           | LCD port segment selection register 4 (LSELS4)                                                                                |       |

|           | LCD port common selections of the common selections and the common selections of the common selections are common selections. |       |

| 20.2.10   | 25-18                                                                                                                         |       |

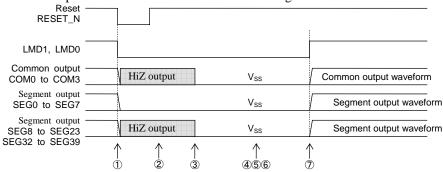

| 25.3 De   | escription of Operation                                                                                                       | 25-19 |

|           | Operation of LCD Drivers and Bias Generation Circuit                                                                          |       |

|           | Display Register Segment Map                                                                                                  |       |

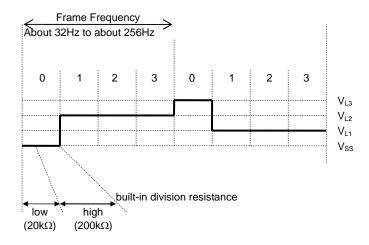

|           | Built-in division resistance for LCD drive voltage generation                                                                 |       |

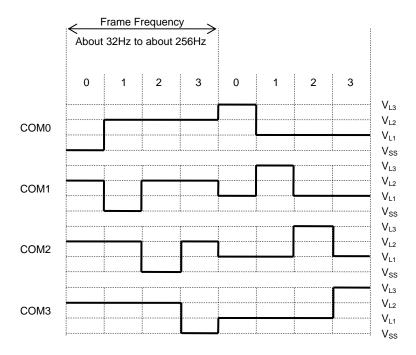

|           | Common Output Waveforms for 1/4 duty and 1/3 bias                                                                             |       |

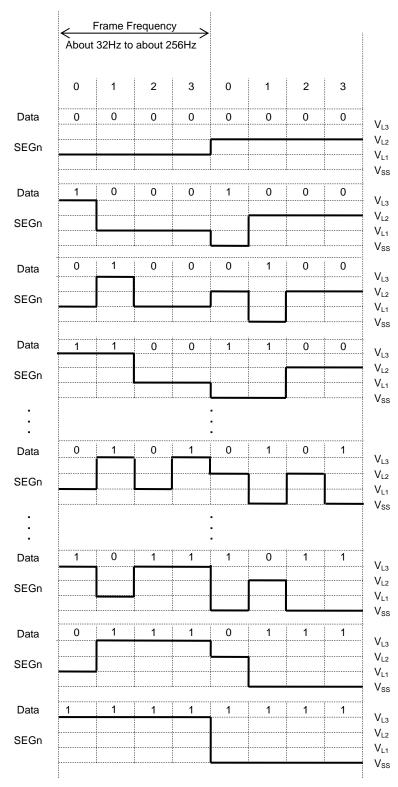

|           | Segment Output Waveform for 1/4 duty and 1/3 bias                                                                             |       |

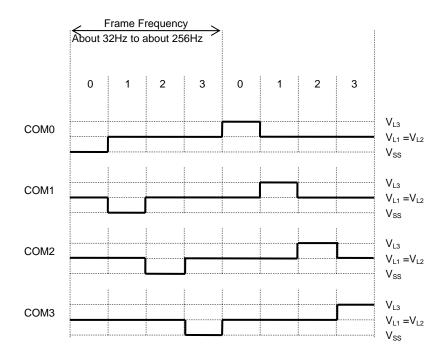

|           | Common Output Waveforms for 1/4 duty and 1/2 bias                                                                             |       |

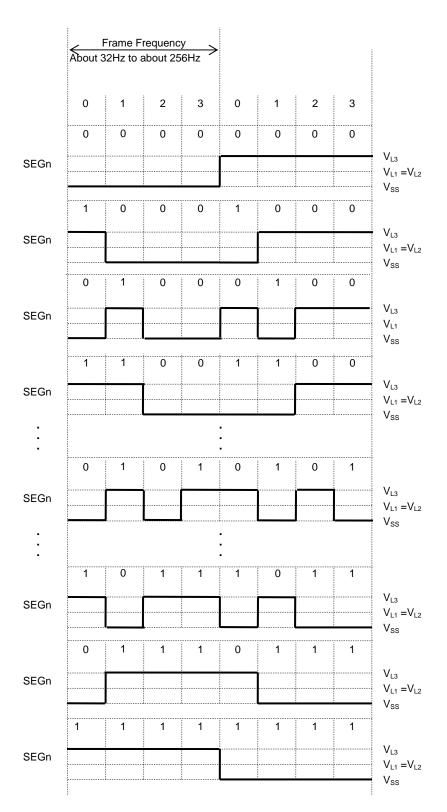

|           | Segment Output Waveform for 1/4 duty and 1/2 bias                                                                             |       |

| 23.3.7    | beginent output waveform for 1/1 duty and 1/2 olds                                                                            |       |

| Chapter 2 | 6                                                                                                                             |       |

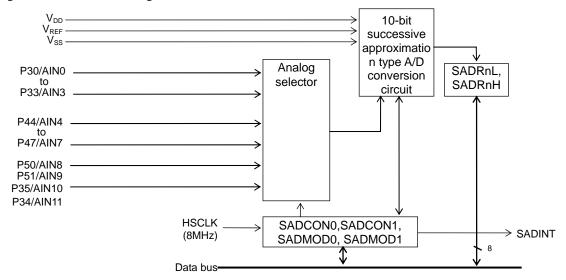

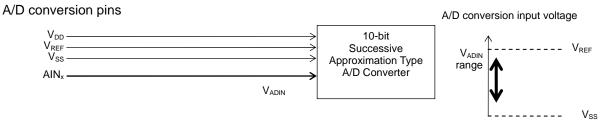

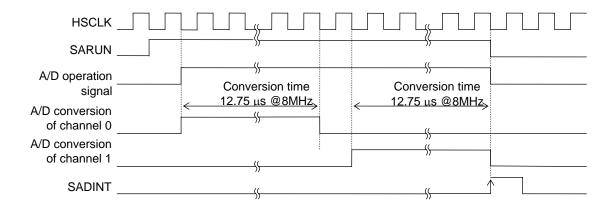

| 26. Succ  | essive Approximation Type A/D Converter (SA-ADC)                                                                              | 26-1  |

|           | verview                                                                                                                       |       |

|           | Features                                                                                                                      |       |

|           | Configuration                                                                                                                 |       |

|           | List of Pins                                                                                                                  |       |

|           | escription of Registers                                                                                                       |       |

|           | List of Registers                                                                                                             |       |

|           | SA-ADC Result Register 0L (SADR0L)                                                                                            |       |

|           | SA-ADC Result Register 0H (SADR0H)                                                                                            |       |

|           | SA-ADC Result Register 1L (SADR1L)                                                                                            |       |

|           | SA-ADC Result Register 1H (SADR1H)                                                                                            |       |

|           | SA-ADC Result Register 2L (SADR2L)                                                                                            |       |

|           | SA-ADC Result Register 2H (SADR2H)                                                                                            |       |

|           | SA-ADC Result Register 3L (SADR3L)                                                                                            |       |

|           | SA-ADC Result Register 3H (SADR3H)                                                                                            |       |

|           | SA-ADC Result Register 4L (SADR4L)                                                                                            |       |

|           | SA-ADC Result Register 4H (SADR4H)                                                                                            |       |

|           | SA-ADC Result Register 5L (SADR5L)                                                                                            |       |

|           | SA-ADC Result Register 5H (SADR5H)                                                                                            |       |

|           | SA-ADC Result Register 6L (SADR6L)                                                                                            |       |

|           | SA-ADC Result Register 6H (SADR6H)                                                                                            |       |

|           | SA-ADC Result Register 7L (SADR7L)                                                                                            |       |

|           | SA-ADC Result Register 7H (SADR7H)                                                                                            |       |

|           | SA-ADC Result Register 8L (SADR8L)                                                                                            |       |

|           | SA-ADC Result Register 8H (SADR8H)                                                                                            |       |

|           | SA-ADC Result Register 9L (SADR9L)                                                                                            |       |

|           | SA-ADC Result Register 9H (SADR9H)                                                                                            |       |

|           | SA-ADC Result Register AL (SADRAL)                                                                                            |       |

|           | SA-ADC Result Register AH (SADRAH)                                                                                            |       |

|           | SA-ADC Result Register BL (SADRBL)                                                                                            |       |

|           | SA-ADC Result Register BH (SADRBH)                                                                                            |       |

|           | SA-ADC Control Register 0 (SADCON0)                                                                                           |       |

|           | SA-ADC Control Register 1 (SADCON1)                                                                                           |       |

| _05       |                                                                                                                               | 20 17 |

| 26.2.36 SA-ADC Mode Register 0 (SADMOD0)                        | 26-18 |

|-----------------------------------------------------------------|-------|

| 26.2.37 SA-ADC Mode Register 1 (SADMOD1)                        |       |

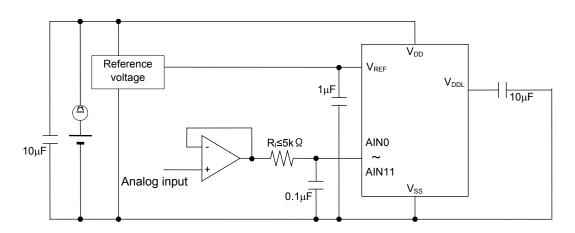

| 26.3 Description of Operation                                   | 26-21 |

| 26.3.1 Setup of the A/D conversion channel                      | 26-21 |

| 26.3.2 Operation of Successive Approximation Type A/D Converter | 26-22 |

| Chapter 27                                                      |       |

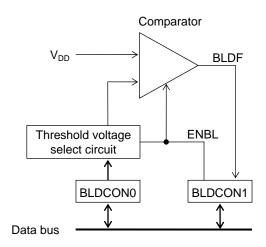

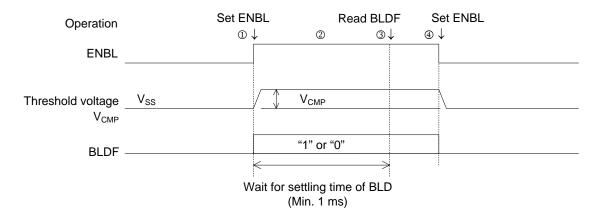

| 27. Battery Level Detector                                      | 27-1  |

| 27.1 Overview                                                   |       |

| 27.1.1 Features                                                 | 27-1  |

| 27.1.2 Configuration                                            | 27-1  |

| 27.2 Description of Registers                                   | 27-2  |

| 27.2.1 List of Registers                                        |       |

| 27.2.2 Battery Level Detector Control Register 0 (BLDCON0)      |       |

| 27.2.3 Battery Level Detector Control Register 1 (BLDCON1)      |       |

| 27.3 Description of Operation                                   |       |

| 27.3.1 Threshold Voltage                                        |       |

| 27.3.2 Operation of Battery Level Detector                      | 27-6  |

| Chapter 28                                                      |       |

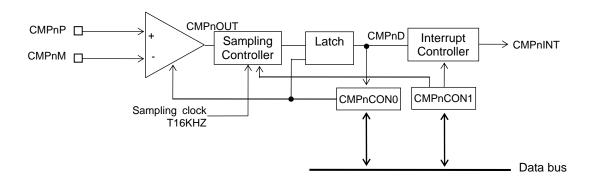

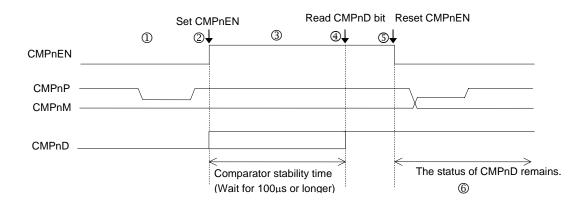

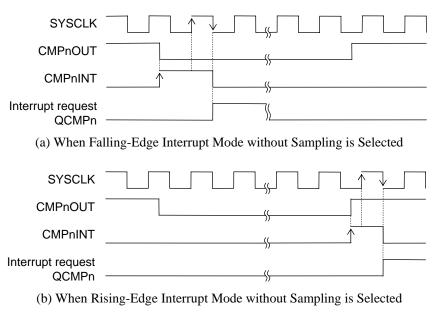

| 28. Analog Comparator                                           | 28-1  |

| 28.1 Overview                                                   | 28-1  |

| 28.1.1 Features                                                 | 28-1  |

| 28.1.2 Configuration                                            | 28-1  |

| 28.1.3 List of Pins                                             |       |

| 28.2 Description of Registers                                   |       |

| 28.2.1 List of Registers                                        |       |

| 28.2.2 Comparator Control Register 0 (CMP0CON0)                 |       |

| 28.2.3 Comparator Control Registers 1 (CMP0CON1)                |       |

| 28.2.4 Comparator1 Control Register 0 (CMP1CON0)                |       |

| 28.2.5 Comparator Control Registers 1 (CMP1CON1)                |       |

| 28.3 Description of Operation                                   |       |

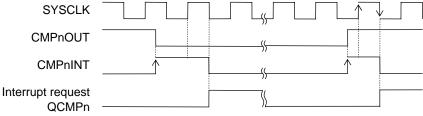

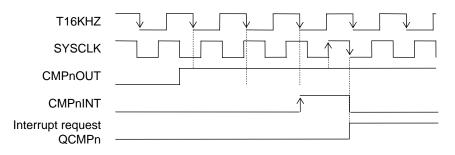

| 28.3.1 Analog Comparator Function                               |       |

|                                                                 | 20 0  |

| Chapter 29                                                      |       |

| 29. Power Supply Circuit                                        |       |

| 29.1 Overview                                                   |       |

| 29.1.1 Features                                                 |       |

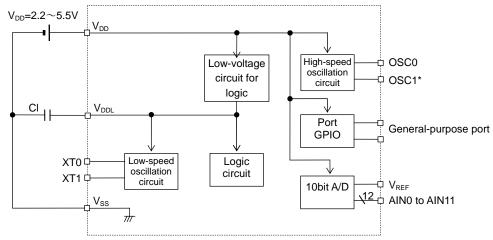

| 29.1.2 Configuration                                            |       |

| 29.1.3 List of Pins                                             |       |

| 29.2 Description of Operation                                   |       |

| Chapter 30                                                      |       |

| 30. Flash Memory Programming                                    | 30-1  |

| 30.1 Overview                                                   |       |

| 30.1.1 Features                                                 | 30-1  |

| 30.2 Description of Registers                                   | 30-2  |

| 30.2.1 List of Registers                                        |       |

| 30.2.2 Flash Address Register L,H (FLASHAL,H)                   |       |

| 30.2.3 Flash Data Register L,H (FLASHDL,H)                      |       |

| 30.2.4 Flash Control Register (FLASHCON)                        |       |

| 30.2.5 Flash Acceptor (FLASHACP)                                |       |

| 30.2.6 Flash Segment Register (FLASHSEG)                        |       |

| 30.2.7 Flash Self Register (FLASHSLF)                           | 30-8  |

| 30.2.8     | Flash Remap Register (REMAPADD)                | 30-9  |

|------------|------------------------------------------------|-------|

|            | scription of Operation                         |       |

|            | Block Erase Function                           |       |

| 30.3.2     | Sector Erase Function                          | 30-13 |

| 30.3.3     | 1-word Write Function                          | 30-14 |

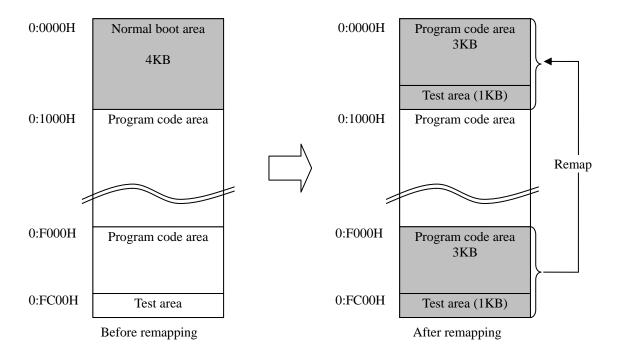

| 30.3.4     | Remap function by software                     | 30-15 |

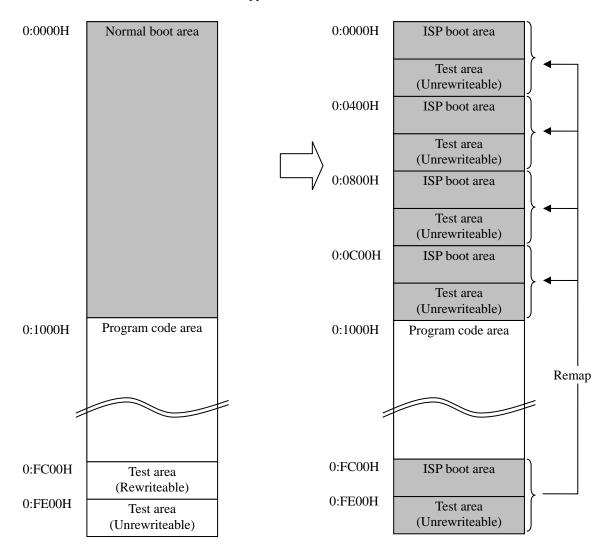

|            | Remap function by hardware (external terminal) |       |

| 30.3.6     | Notes in Use                                   | 30-17 |

| Chapter 3  | 1                                              |       |

| 31. On-C   | hip Debug Function                             | 31-1  |

|            | erview                                         |       |

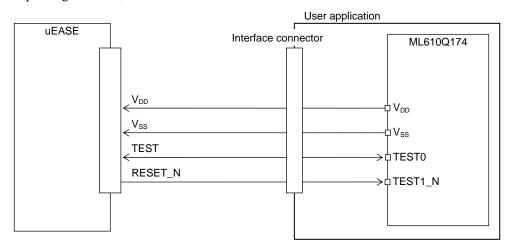

|            | w to Connect the On-Chip Debug Emulator        |       |

| Chapter 32 | 2                                              |       |

| 32. Code-  | Option                                         | 32-1  |

| 32.1 Ov    | erview                                         | 32-1  |

| 32.1.1     | Features                                       | 32-1  |

|            | scription of Registers                         |       |

|            | List of Registers                              |       |

|            | Code-Option Register (CODEOP0)                 |       |

|            | e method of a setup of Code-Option data        |       |

|            | The format of Code-Option data                 |       |

| 32.3.2     | The method of programming of Code-Option data  | 32-4  |

| Appendixe  | es es                                          |       |

| Appendix   |                                                |       |

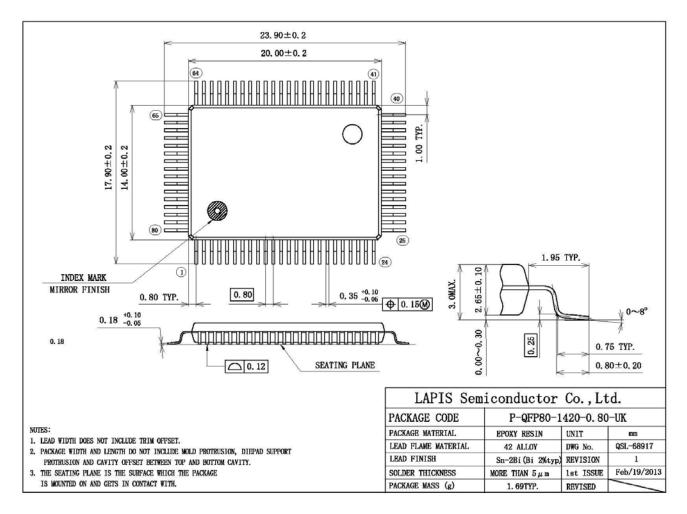

| Appendix   | B Package Dimensions                           | B-1   |

| Appendix   | C Electrical Characteristics                   |       |

| Appendix   |                                                |       |

| Appendix   | E Check List                                   | E-1   |

| Revision I | History                                        |       |

| Revision F | History                                        | R-1   |

# Chapter 1

# **Overview**

#### Overview

#### 1.1 Features

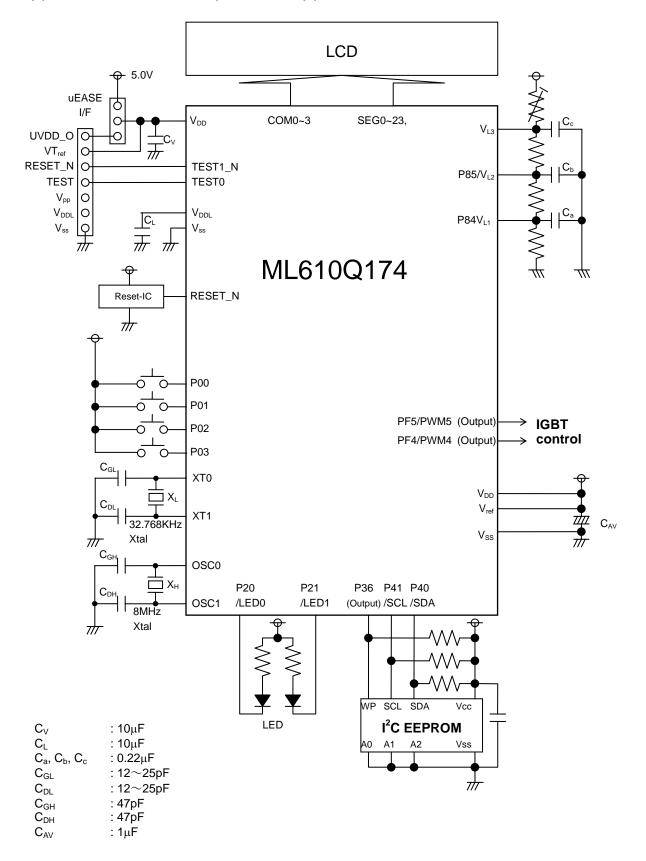

This LSI is a high-performance 8-bit CMOS microcontroller into which rich peripheral circuits, such as 10-bit A/D converter, timer, PWM, synchronous serial port, UART, I2C bus interface (master), Battery level detect circuit, LCD driver, are incorporated around 8-bit CPU nX-U8/100.

The CPU nX-U8/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by 3-stage pipe line architecture parallel processing.

The on-chip debug function that is installed enables program debugging and programming.

#### CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction system: 16-bit instructions

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on

- On-Chip debug function

- Minimum instruction execution time

Approx 30.5 µs (at 32.768kHz system clock)

Approx 0.122  $\mu s$  (at 8.192MHz system clock)@DV<sub>DD</sub> = 2.2 to 5.5V

#### Internal memory

- Internal 128-Kbyte flash ROM(64K × 16-bit) (including unusable 1KByte TEST area)

- Internal 2-Kbyte Data Flash  $(1-Kbyte \times 2)$

- Internal 4-Kbyte RAM (4096 × 8 -bit)

#### • Interrupt controller

- 1 non-maskable interrupt sources (Internal source: 1, External source: 1)

- 26 maskable interrupt sources (Internal source: 22, External source: 4)

#### • Time base counter

- Low-speed time base counter × 1 channel

- High-speed time base counter × 1 channel

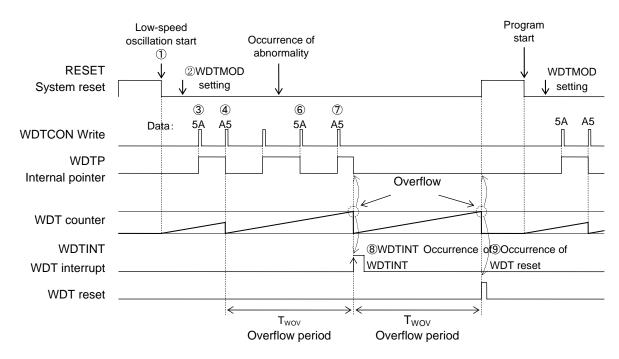

#### · Watchdog timer

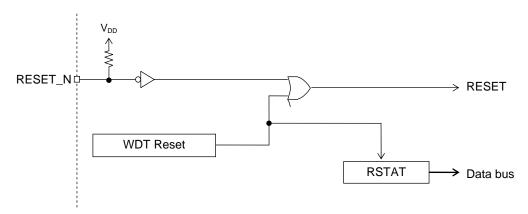

- Generates a non-maskable interrupt upon the first overflow and a system reset occurs upon the second

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, and 8s)

#### Timers

8 bits × 6ch (16-bit configuration available)

#### PWM

Resolution 16 bits × 3 channel(IGBT control)

FEUL610Q174-01

- Synchronous serial port

- 2ch

- Master/slave selectable

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- UART

- Half-duplex

- TXD/RXD  $\times$  2 channels

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit /2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

- I<sup>2</sup>C bus interface

- Master function only

- Fast mode(400kbps@8MHz), Standard mode (100kbps@8MHz)

- Successive approximation type A/D converter

- 10-bit A/D converter

- Input: 12ch (Maximum)

- Conversion time: 12.75µs per channel

- Analog Comparator

- 2ch

- Interrupt allow edge selection and sampling selection

- General-purpose ports 61 (Maximum)

- Input-only port × 6ch

- Output-only port × 6ch (including secondary functions)

- Input/output × 19ch (including secondary functions)

- Input/output × 30ch (including LCD driver functions)

- LCD driver

- 128 dots maximum. (32seg  $\times$  4 com), 1/1 to 1/4 duty

- Frame frequency selectable (approx. 64 Hz, 73 Hz, 85 Hz, and 102 Hz, 32Hz, 128Hz, 171Hz, 256Hz)

- LCD drive stop mode, LCD display mode, all LCDs on mode, and all LCDs off mode selectable

- Power supply for LCD drivers selectable (external division resistance, built-in division resistance)

- Battery level detect function

- Judgment voltages: One of 4 levels

- Judgment accuracy: ±2% (Typ.)

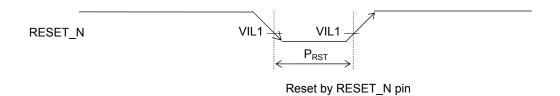

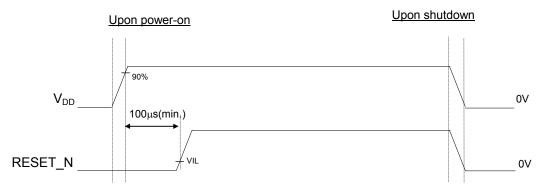

- Reset

- Reset through the RESET\_N pin

- Reset by the watchdog timer (WDT) overflow

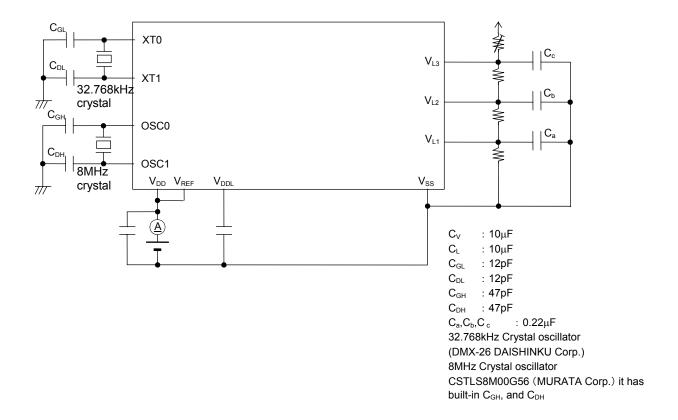

- Clock

- Low-speed clock:

- Crystal oscillation (32.768 kHz), Built-in RC oscillation (32.7kHz)

- High-speed clock

- Built-in oscillation (8.192MHz/8MHz), Crystal / ceramic oscillation (8MHz), external clock

#### • Power management

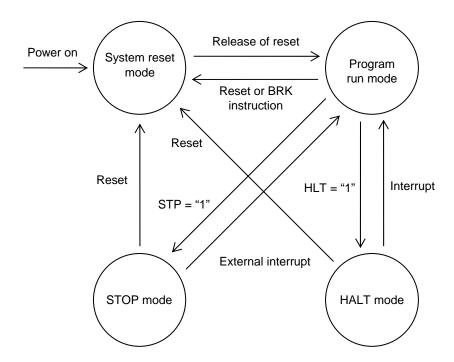

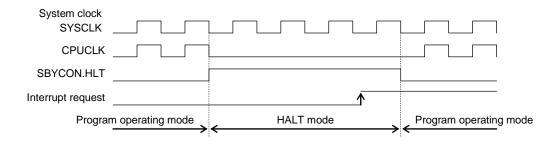

- HALT mode: Instruction execution by CPU is suspended (peripheral circuits are in operating states).

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, or 1/8 of the oscillation clock)

- Block control function: Operation of an intact functional block circuit is powerd down. (register reset and clock stop)

#### Shipment

- 80-pin QFP (QFP80-P-1420-0.80)

- ML610Q174-xxxGA (blank product: ML610Q174-NNNGA)

xxx: ROM code number

- Guaranteed operating range

- Operating temperature: -40°C to 85°C

- Operating voltage:  $V_{DD} = 2.2V$  to 5.5V,  $V_{REF} = 4.5V$  to 5.5V

## 1.2 Configuration of Functional Blocks

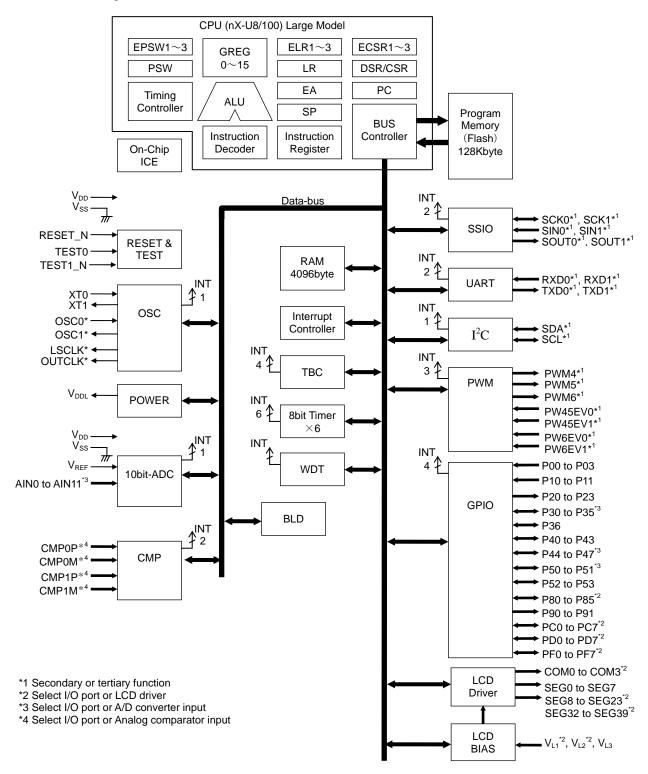

### 1.2.1 Block Diagram of ML610Q174

Figure 1-1 Block Diagram of ML610Q174

#### 1.3 Pins

#### 1.3.1 Pin Layout

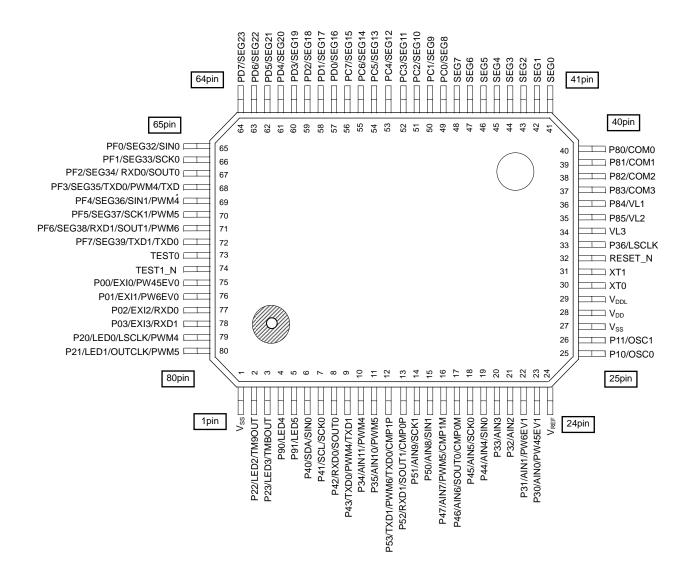

#### 1.3.1.1 Pin Layout of ML610Q174 QFP Package

Figure 1-3 Pin Layout of ML610Q174 Package

### 1.3.2 List of Pins

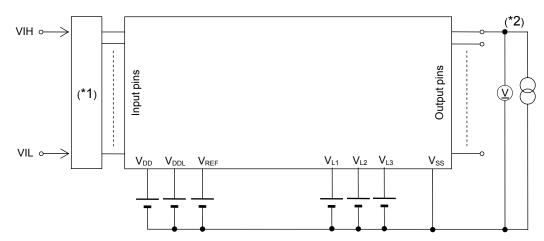

Table 1-1 lists the pins. In the I/O column, "—" denotes a power supply pin (for primary functions only), "I" an input pin, "O" an output pin, and "I/O" an input/output pin.

| and 1/0 | O" an input/             | outpu | t pin.                                                                      |             |        |                                  |             |         |               |

|---------|--------------------------|-------|-----------------------------------------------------------------------------|-------------|--------|----------------------------------|-------------|---------|---------------|

| Pin     |                          | Р     | rimary function                                                             | Sec         | ondary | / function                       | Te          | ertiary | function      |

| No.     | Pin<br>name              | I/O   | Description                                                                 | Pin<br>name | I/O    | Description                      | Pin<br>name | I/O     | Description   |

| 1,27    | Vss                      |       | Negative power supply pin                                                   | 1           |        | _                                |             | _       |               |

| 28      | $V_{DD}$                 | _     | Positive power supply pin                                                   | _           | _      | _                                | _           |         |               |

| 29      | $V_{DDL}$                | _     | Power supply for internal logic (internally generated)                      | _           | _      | _                                | _           | _       | _             |

| 34      | $V_{L3}$                 | _     | Power supply pin for LCD bias                                               | _           | _      | _                                | _           | _       | _             |

| 73      | TEST0                    | I/O   | Input/output pin for testing                                                | _           | _      | _                                | _           | —       | _             |

| 74      | TEST1_N                  | I/O   | Input/output pin for testing                                                |             | _      | _                                | _           | _       |               |

| 32      | RESET_N                  | I     | Reset input pin                                                             | _           | _      | _                                | _           | _       |               |